ES1650.1 Piggyback Carrier Board User's Guide

# Copyright

The data in this document may not be altered or amended without special notification from ETAS GmbH. ETAS GmbH undertakes no further obligation in relation to this document. The software presented herein is provided on the basis of a general license agreement or a single license. Using and copying is only allowed in concurrence with the specifications stipulated in the contract.

Under no circumstances may any part of this document be copied, reproduced, transmitted, stored in a retrieval system or translated into another language without the express written permission of ETAS GmbH.

#### © Copyright 2000 - 2003 ETAS GmbH, Stuttgart

The names and designations used in this document are trademarks or brands belonging to the respective owners.

R1.0.6 EN - 11.2003

TTN F 00K 700 294

# Contents

| 1 | Introc | duction    |                             | 7  |

|---|--------|------------|-----------------------------|----|

|   | 1.1    | Features   |                             | 7  |

|   | 1.2    | Block Dia  | gram                        | 9  |

|   | 1.3    | ES1650.1   | Hardware                    | 1  |

|   |        | 1.3.1      | Carrier for Piggybacks      | 1  |

|   |        | 1.3.2      | External Local Reset 1      | 1  |

|   | 1.4    | Hardware   | Configuration               | 3  |

|   |        | 1.4.1      | VMEbus Base Address 1       | 3  |

|   |        | 1.4.2      | Size of the Address Range 1 | 6  |

|   |        | 1.4.3      | Address Modifier 1          | 6  |

|   |        | 1.4.4      | Local Reset                 | 6  |

|   | 1.5    | Pin Assigr | nment                       | 7  |

|   | 1.6    | Technical  | Data 1                      | 9  |

| 2 | PB16   | 50DAC1.1   | D/A Piggyback (4 Channels)  | 21 |

|   | 2.1    | Features   |                             | 21 |

|   | 2.2    | Applicatio | ons                         | 21 |

|   | 2.3    | Block Dia  | gram                        | 22 |

|   | 2.4    | PB1650D    | AC1.1 Hardware              | 23 |

|   |        | 2.4.1      | Signal Conditioning 2       | 23 |

|   | 2.5<br>2.6<br>2.7                                     | 2.4.2Output Voltage Range2.4.3Digital/Analog Converter2.4.4Control Interface2.4.5Size of the Address RangeConfigurationPin AssignmentTechnical DataPin Assignment                                                                               | 24<br>24<br>24<br>25<br>26                                                                                                                     |

|---|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 3 | PB16<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7 | 50DIO1.1 Digital I/O Piggyback (8/8 Channels)FeaturesApplicationsBlock DiagramPB1650DIO1.1 Hardware3.4.1 Inputs3.4.2 Outputs3.4.3 Power ON State3.4.4 Control Interface3.4.5 Size of the Address RangeConfigurationPin AssignmentTechnical Data | 29<br>29<br>30<br>31<br>31<br>32<br>33<br>33<br>33<br>34<br>34                                                                                 |

| 4 | PB16<br>4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7 | 50DIO2.1 Digital I/O Piggyback (10/10 Channels)FeaturesApplicationsBlock DiagramPB1650DIO2.1 Hardware4.4.1Inputs4.4.2Outputs4.4.3Power ON State4.4.4Control Interface4.4.5Size of the Address RangeConfigurationPin AssignmentTechnical Data    | <ol> <li>37</li> <li>37</li> <li>38</li> <li>39</li> <li>39</li> <li>40</li> <li>41</li> <li>41</li> <li>41</li> <li>42</li> <li>42</li> </ol> |

| 5 | PB165<br>5.1<br>5.2<br>5.3<br>5.4                     | 50ADC1.1 A/D Piggyback (8 Channels).<br>Features<br>Applications<br>Block Diagram<br>PB1650ADC1.1 Hardware                                                                                                                                      | 47<br>47<br>48                                                                                                                                 |

|   |       | 5.4.1      | Signal Conditioning                | 49 |

|---|-------|------------|------------------------------------|----|

|   |       | 5.4.2      | Input Voltage Range and Gain       | 50 |

|   |       | 5.4.3      | A/D Converter                      | 50 |

|   |       | 5.4.4      | Control Logic                      | 50 |

|   |       | 5.4.5      | ID Byte                            | 50 |

|   |       | 5.4.6      | Size of the Address Range          | 50 |

|   | 5.5   | Configura  | ation                              | 50 |

|   |       | 5.5.1      | Input Voltage Range                | 51 |

|   |       | 5.5.2      | Offset Voltage                     | 52 |

|   | 5.6   | Pin Assigr | nment                              | 52 |

|   | 5.7   | Technical  | Data                               | 54 |

| 6 | PB165 | 50REL1.1 F | elay Piggyback (8 Channels)        | 55 |

|   | 6.1   |            |                                    |    |

|   | 6.2   |            | ons                                |    |

|   | 6.3   | Block Dia  | gram                               | 56 |

|   | 6.4   | PB1650RI   | EL1.1 Hardware                     | 57 |

|   |       | 6.4.1      | Relays                             | 57 |

|   |       | 6.4.2      | Output Voltage Range               | 57 |

|   |       | 6.4.3      | ID Byte                            | 58 |

|   |       | 6.4.4      | Size of the Address Range          | 58 |

|   | 6.5   | Configura  | ation                              | 58 |

|   | 6.6   | Pin Assigr | nment                              | 58 |

|   | 6.7   | Technical  | Data                               | 59 |

| 7 | PB165 | 50PRT1.1 F | Prototyping Piggyback              | 61 |

|   | 7.1   |            |                                    |    |

|   | 7.2   | Applicatio | ons                                | 61 |

|   | 7.3   | PB1650PF   | RT1.1 Hardware                     | 65 |

|   |       | 7.3.1      | Supply Voltages                    | 66 |

|   |       | 7.3.2      | VMEbus Interface                   | 67 |

|   |       | 7.3.3      | Dual-Ported RAM Access             | 67 |

|   |       | 7.3.4      | Size of the Address Range          | 68 |

|   | 7.4   | Configura  | ation                              | 68 |

|   |       | 7.4.1      | B501 Jumper                        | 69 |

|   |       | 7.4.2      | JP1 Jumper                         | 69 |

|   |       | 7.4.3      | JP2 Jumper                         | 69 |

|   |       | 7.4.4      | ST4 Jumper Strip                   | 70 |

|   | 7.5   | Pin Assigr | nment                              | 71 |

|   |       | 7.5.1      | ES1650.1 X1 Front-Facing Connector | 71 |

|   |       | 7.5.2      | WRAP1 Connector                    | 76 |

|   |        | 7.5.4       | WRAP2 (<br>WRAP4 ( | Connect | or | <br> | <br> | <br> | <br> | <br>79 |

|---|--------|-------------|--------------------|---------|----|------|------|------|------|--------|

|   |        | 7.5.5       | 51500 00           |         |    |      |      |      |      |        |

|   | 7.6    | Technica    | Data               |         |    | <br> | <br> | <br> | <br> | <br>81 |

| 8 | ETAS   | Contact A   | ddresses .         |         |    | <br> | <br> | <br> | <br> | <br>83 |

|   | List o | f Figures . |                    |         |    | <br> | <br> | <br> | <br> | <br>85 |

|   | List o | f Tables    |                    |         |    | <br> | <br> | <br> | <br> | <br>87 |

|   | Index  |             |                    |         |    | <br> | <br> | <br> | <br> | <br>89 |

# 1 Introduction

This section contains information about the basic features and applications of the ES1650.1 Piggyback Carrier Board. A block diagram shows the schematic layout of the board.

#### note

Some components of the board may be damaged or destroyed by electrostatic discharges. Please keep the board in its storage package until it is installed. The board should only be taken from its storage package, configured and installed at a work place that is protected against static discharge.

#### note

The components, connectors, and printed lines of the board may carry dangerous high voltages.

These voltages may even exist when the board is not installed in the VME system or when the VME system is powered off. Make sure that the board is protected against contact during its operation.

Disconnect all connections to the ES1650.1 Piggyback Carrier Board before removing the board from the VME system.

#### 1.1 Features

The ES1650.1 Piggyback Carrier Board is used in VMEbus systems as a carrier board for piggybacks. The board can hold two piggybacks. There are piggybacks for a variety of tasks, such as digital and analog input and output modules as well as relay modules with switching capability.

The piggybacks are connected to the carrier board via connector sockets. The ports of the piggybacks are provided on the front panel via a 50-pin connector. The signal pins of the front panel connector are electrically isolated from the VMEbus.

The carrier board has a VMEbus slave interface - the board can be configured for different address ranges using jumpers.

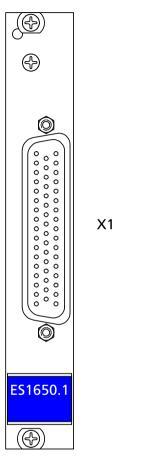

The following figure shows the front panel of the carrier board and the position of the front panel connectors.

Fig. 1-1 ES1650.1 Piggyback Carrier Board Front Panel

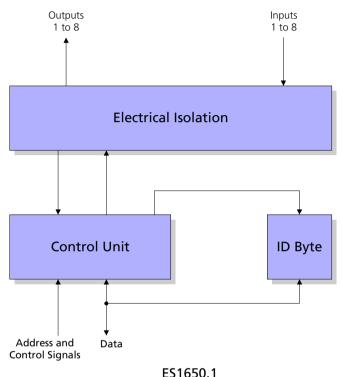

## 1.2 Block Diagram

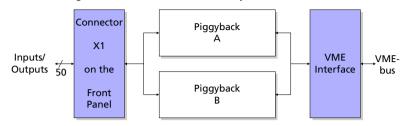

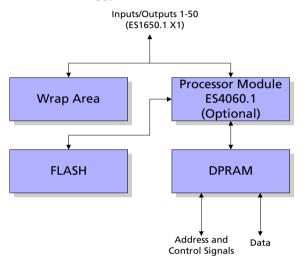

The block diagram illustrates the schematic layout of the board.

#### Fig. 1-2 ES1650.1 Block Diagram

The 50-pin connector is visible on the left side of the front panel. It is wired to the two piggybacks. The VMEbus interface is located on the extreme right. This interface converts the signals of the VMEbus into data, address, and control signals for the piggybacks.

The pins of the front panel connector are electrically isolated from the VMEbus.

## 1.3 ES1650.1 Hardware

This section provides a detailed overview of the features of the ES1650.1 Piggyback Carrier Board. You will find information on the following subjects:

- carrier for piggybacks

- external local reset

#### 1.3.1 Carrier for Piggybacks

The ES1650.1 Piggyback Carrier Board is used in VMEbus systems as a carrier for piggybacks. Piggybacks are available for various analog and digital signal input and output tasks.

On the front panel, the board provides a 50-pin connector for the inputs and outputs of the piggybacks. This connector is electrically isolated from the VME-bus.

On the VMEbus side, the carrier board is responsible for address selection and for buffering the data, address, and control lines of the VMEbus. The ES1650.1 Piggyback Carrier Board is equipped with a slave interface with 24 address lines and 16 data lines. Different size address ranges within the address space of the VMEbus can be assigned to the piggybacks. The base address and the size of the address range are configured by jumpers.

1.3.2 External Local Reset

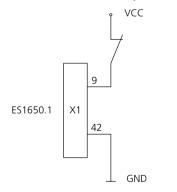

The front panel connector provides two pins that can be used to trigger a local reset of the piggybacks. If you intend to use this function, these two pins need to be connected to a relay.

Fig. 1-3 Relay for the Local Reset

The local reset is triggered when the connection between the two pins is interrupted. The pins, however, have to be supplied with 5 V < VCC < 48 V. The reset only affects the piggybacks and *not* the VMEbus.

#### note

If pins 9 and 42 of the front-facing connector X1 remain disconnected and the external reset was triggered by jumper B20, there can be a sporadic reset of the piggybacks.

Connect pins 1 and 2 of jumper B20 if you are not using the external reset and leave pins 9 and 42 disconnected.

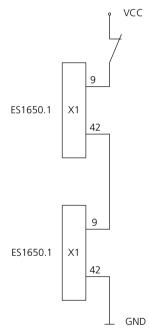

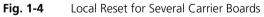

If you use more than one ES1650.1 Piggyback Carrier Board in a system and wish to use a common local reset for all boards, you can connect the corresponding pins of the boards in series with the relays.

A jumper can be used to disable the function of the two front panel pins so that an external local reset cannot be triggered.

# 1.4 Hardware Configuration

This section contains information on configuring the jumpers of the ES1650.1 Piggyback Carrier Board. The jumpers are used to configure the following settings:

- VMEbus base address and size of address range

- address modifier

- local reset

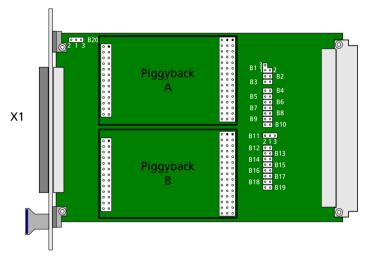

The figure shows the position of the jumpers and connector sockets for the piggybacks.

## 1.4.1 VMEbus Base Address

The base address of the ES1650.1 Piggyback Carrier Board is selected by the five jumpers B2, B12, B13, B14, and B15.

#### note

Make sure that the address range of the ES4120 board does **not** overlap address ranges of other boards in your system.

If you chose an address block size of 256 bytes, you can use 32 different address settings in the range \$FE0400 to \$FEFC00. For an address block size of 8 KBytes, jumpers B14 and B15 are ignored. This provides only eight address settings. The default base address of the board is \$FE0400.

#### note

A closed jumper means logical "0"; an open jumper means logical "1".

| Jumper | Address | Default Setting |

|--------|---------|-----------------|

| B2     | A15     | Closed          |

| B12    | A14     | Closed          |

| B13    | A13     | Closed          |

| B14    | A12     | Closed          |

| B15    | A11     | Closed          |

Tab. 1-1

Assignment of Jumper and Address Line

The following table provides you with an overview of the configuration of jumpers B2, and B12 to B16 for the base addresses of the 256-byte blocks. "o" stands for an open jumper; "c" for a closed jumper.

| Address Range       | B2 | B12 | B13 | B14 | B15 | B16 |

|---------------------|----|-----|-----|-----|-----|-----|

| 0xFE0400 - 0xFE04FF | с  | с   | с   | с   | с   | 0   |

| 0xFE0C00 - 0xFE0CFF | с  | с   | с   | С   | 0   | 0   |

| 0xFE1400 - 0xFE14FF | С  | с   | с   | 0   | С   | 0   |

| 0xFE1C00 - 0xFE1CFF | с  | с   | с   | 0   | 0   | 0   |

| 0xFE2400 - 0xFE24FF | с  | с   | 0   | с   | с   | 0   |

| 0xFE2C00 - 0xFE2CFF | с  | с   | 0   | с   | 0   | 0   |

| 0xFE3400 - 0xFE34FF | с  | с   | 0   | 0   | с   | 0   |

| 0xFE3C00 - 0xFE3CFF | с  | с   | 0   | 0   | 0   | 0   |

| 0xFE4400 - 0xFE44FF | с  | 0   | с   | с   | с   | 0   |

| 0xFE4C00 - 0xFE4CFF | с  | 0   | с   | с   | 0   | 0   |

| 0xFE5400 - 0xFE54FF | с  | 0   | с   | 0   | с   | 0   |

| 0xFE5C00 - 0xFE5CFF | с  | 0   | с   | 0   | 0   | 0   |

| 0xFE6400 - 0xFE64FF | с  | 0   | 0   | с   | с   | 0   |

| 0xFE6C00 - 0xFE6CFF | с  | 0   | 0   | с   | 0   | 0   |

| 0xFE7400 - 0xFE74FF | с  | 0   | 0   | 0   | с   | 0   |

**Tab. 1-2**Base Address and Jumper Configuration

| Address Range       | B2 | B12 | B13 | B14 | B15 | B16 |

|---------------------|----|-----|-----|-----|-----|-----|

| 0xFE7C00 - 0xFE7CFF | с  | 0   | 0   | 0   | 0   | 0   |

| 0xFE8400 - 0xFE84FF | 0  | с   | с   | с   | с   | 0   |

| 0xFE8C00 - 0xFE8CFF | 0  | с   | с   | с   | 0   | 0   |

| 0xFE9400 - 0xFE94FF | 0  | с   | с   | 0   | с   | 0   |

| 0xFE9C00 - 0xFE9CFF | 0  | с   | с   | 0   | 0   | 0   |

| 0xFEA400 - 0xFEA4FF | 0  | с   | 0   | с   | с   | 0   |

| 0xFEAC00 - 0xFEACFF | 0  | с   | 0   | с   | 0   | 0   |

| 0xFEB400 - 0xFEB4FF | 0  | с   | 0   | 0   | с   | 0   |

| 0xFEBC00 - 0xFEBCFF | 0  | с   | 0   | 0   | 0   | 0   |

| 0xFEC400 - 0xFEC4FF | 0  | 0   | с   | с   | с   | 0   |

| 0xFECC00 - 0xFECCFF | 0  | 0   | с   | с   | 0   | 0   |

| 0xFED400 - 0xFED4FF | 0  | 0   | с   | 0   | с   | 0   |

| 0xFEDC00 - 0xFEDCFF | 0  | 0   | с   | 0   | 0   | 0   |

| 0xFEE400 - 0xFEE4FF | 0  | 0   | 0   | с   | с   | 0   |

| 0xFEEC00 - 0xFEECFF | 0  | 0   | 0   | с   | 0   | 0   |

| 0xFEF400 - 0xFEF4FF | 0  | 0   | 0   | 0   | с   | 0   |

| 0xFEFC00 - 0xFEFCFF | 0  | 0   | 0   | 0   | 0   | 0   |

Tab. 1-2

Base Address and Jumper Configuration (cont'd)

The following table shows you the configuration of jumpers B2, and B12 to B16 for the base addresses of the 8-KByte blocks. "o" stands for an open jumper; "c" for a closed jumper. Jumpers marked with "x" are not evaluated.

| Address Range       | B2 | B12 | B13 | B14 | B15 | B16 |

|---------------------|----|-----|-----|-----|-----|-----|

| 0xFE0000 - 0xFE1FFF | с  | с   | с   | х   | х   | с   |

| 0xFE2000 - 0xFE3FFF | с  | с   | 0   | х   | х   | с   |

| 0xFE4000 - 0xFE5FFF | с  | 0   | с   | х   | х   | с   |

| 0xFE6000 - 0xFE7FFF | с  | 0   | 0   | х   | х   | с   |

| 0xFE8000 - 0xFE9FFF | 0  | с   | с   | х   | х   | с   |

| 0xFEA000 - 0xFEBFFF | 0  | с   | 0   | х   | х   | с   |

| 0xFEC000 - 0xFEDFFF | 0  | 0   | с   | х   | х   | с   |

| OxFEE000 - OxFEFFFF | 0  | 0   | 0   | х   | х   | с   |

Tab. 1-3

Base Address and Jumper Configuration

#### 1.4.2 Size of the Address Range

The size of the address range occupied by the ES1650.1 Piggyback Carrier Board in your system is selected by jumper B16. You can choose between the sizes 265 bytes and 8 KBytes. The size that needs to be set depends on the piggybacks used.

| Jumper | Open                          | Closed  |

|--------|-------------------------------|---------|

| B16    | 256-byte<br>(default setting) | 8-KByte |

#### 1.4.3 Address Modifier

The B3 jumper determines the address modifier. You can choose between the access types "Short Access" (29/2D) and "Standard Access" (39/3D/00)

| Jumper | Open                                 | Closed       |

|--------|--------------------------------------|--------------|

| B3     | Standard Access<br>(default setting) | Short Access |

#### 1.4.4 Local Reset

You can trigger a local reset of the piggybacks by using an external connector pin on the front panel. Use jumper B20 to specify whether this external connector pin is to be evaluated.

| Jumper                 | Source of the Interrupt Vector    |

|------------------------|-----------------------------------|

| B20 open               | Setting not allowed               |

| B20 pins 1-2<br>closed | External local reset not possible |

| B20 pins 1-3<br>closed | External local reset possible     |

#### note

Either pins 1-2 or 1-3 of the B20 jumper **must** be connected. If both jumpers are open, the local reset may be triggered by accident.

## 1.5 Pin Assignment

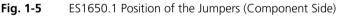

This section describes the pin assignments of the ES1650.1 Piggyback Carrier Board.

X1

In the table below, the letter in the "Piggyback Pin" column indicates the position of the piggyback. "A" designates the upper, "B" the lower piggyback. The number following the letter indicates the pin number of the frontal connector plug for the particular piggyback. The tables with the pin assignments of the piggybacks can be found in the relevant documentation for the individual piggybacks.

| X1 Pin | Piggyback Pin | X1 Pin | Piggyback Pin |

|--------|---------------|--------|---------------|

| 1      | B24           | 26     | A24           |

| 2      | B21           | 27     | A21           |

| 3      | B18           | 28     | A18           |

| 4      | B15           | 29     | A15           |

| 5      | B12           | 30     | A12           |

| 6      | В9            | 31     | A9            |

| 7      | B6            | 32     | A6            |

|        |               |        |               |

Tab. 1-4ES1650.1 Pin Assignment

| X1 Pin  | Piggyback Pin                | X1 Pin | Piggyback Pin  |

|---------|------------------------------|--------|----------------|

| 8       | B3                           | 33     | A3             |

| 9       | Ext. reset<br>supply voltage | 34     | B23            |

| 10      | A23                          | 35     | B20            |

| 11      | A20                          | 36     | B17            |

| 12      | A17                          | 37     | B14            |

| 13      | A14                          | 38     | B11            |

| 14      | A11                          | 39     | B8             |

| 15      | A8                           | 40     | B5             |

| 16      | A5                           | 41     | B25, B26       |

| 17      | A25, A26                     | 42     | Ext. reset GND |

| 18      | B22                          | 43     | A22            |

| 19      | B19                          | 44     | A19            |

| 20      | B16                          | 45     | A16            |

| 21      | B13                          | 46     | A13            |

| 22      | B10                          | 47     | A10            |

| 23      | B7                           | 48     | A7             |

| 24      | B4                           | 49     | A4             |

| 25      | B1, B2                       | 50     | A1, A2         |

| Tab 1_1 | ES1650 1 Pin Accimpont       |        |                |

Tab. 1-4 ES1650.1 Pin Assignment

#### note

The components as well as the component and solder sides of the ES1650.1 Piggyback Carrier Board and its piggybacks may carry dangerous high voltages. These dangerous voltages may even exist if the VMEbus system is powered off or the ES1650.1 Piggyback Carrier Board has been removed. Be sure to disconnect the front panel connector of the ES1650.1 Piggyback Car-

rier Board before removing the board or touching the removed board!

# 1.6 Technical Data

This section contains the technical data of the ES1650.1 Piggyback Carrier Board in tabular form.

VMEbus

| Туре                   | Slave interface                                                      |

|------------------------|----------------------------------------------------------------------|

| Address and data lines | 24-bit address and 16-bit data, or<br>16-bit address and 16-bit data |

| Base address           | \$FE0400 to \$FEFC00 selected by jumpers                             |

| Address modifier       | Standard or short supervisor/user data                               |

## Power Supply

| Basic board | +5 V DC, ±5 %, max. 140 mA without piggybacks |

|-------------|-----------------------------------------------|

# Environmental Conditions

| Ambient temperature during operation | 0 °C to +70 °C             |

|--------------------------------------|----------------------------|

| Storage temperature                  | -55 °C to +85 °C           |

| Relative humidity                    | 5 to 95 %, no condensation |

#### Connectors

| Backplane   | 96-pin DIN 41612 C                                                                                     |

|-------------|--------------------------------------------------------------------------------------------------------|

| Front panel | 50-pin Submin-D socket strip                                                                           |

| Piggybacks  | One 26-pin connector at the front and<br>one 45-pin connector at the VMEbus side<br>for each piggyback |

Physical Dimensions

| Circuit board | 100 x 160 mm²                        |  |

|---------------|--------------------------------------|--|

| Front panel   | Height: 3 U<br>Width: 4 HP (20.3 mm) |  |

# 2 PB1650DAC1.1 D/A Piggyback (4 Channels)

This section contains information about the basic features and applications of the PB1650DAC1.1 D/A piggyback. A block diagram shows the schematic layout of the module.

#### note

Some components of the piggyback may be damaged or destroyed by electrostatic discharges. Please keep the piggyback in its storage package until it is installed.

The piggyback should only be taken from its storage package, configured and installed at a work place that is protected against static discharge.

#### 2.1 Features

The PB1650DAC1.1 piggyback is used to generate analog output signals in VMEbus systems in conjunction with the ES1650.1 Piggyback Carrier Board. The module has the following features:

- digital/analog conversion with 12-bit resolution

- four optional unipolar or bipolar output channels

- its own control interface and ID byte

- separately programmable reference voltage for each channel

- analog output channels electrically isolated from the VMEbus system

#### 2.2 Applications

The PB1650DAC1.1 is used in conjunction with the ES1650.1 Piggyback Carrier Board in VMEbus systems to generate earth-free analog output voltages.

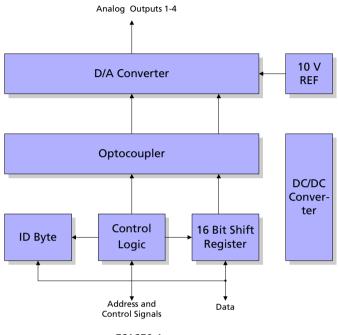

## 2.3 Block Diagram

The block diagram below illustrates the working principle of the piggyback.

ES1650.1

At the bottom left of the block diagram, you see the control interface of the piggyback that on the one hand is connected with the VMEbus and passes data and the clock signal to the digital/analog converter through an optocoupler. Signals are transferred between the VMEbus and the piggyback via the 16-bit shift register at the bottom right of the diagram. The D/A converter at the top of the diagram has eight output channels: four output channels are used to generate the reference voltages for a channel and the other four are used to generate the required analog voltage. The outputs can be used in unipolar or bipolar mode.

# 2.4 PB1650DAC1.1 Hardware

This section gives you a detailed overview of the features of the PB1650DAC1.1 piggyback. You will find information on the following subjects:

- signal conditioning

- output voltage range

- digital/analog converter

- control interface

- size of the address range

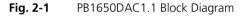

The following figure shows the position of the components of the PB1650DAC1.1 piggyback.

Fig. 2-2 Component Side of the PB1650DAC1.1

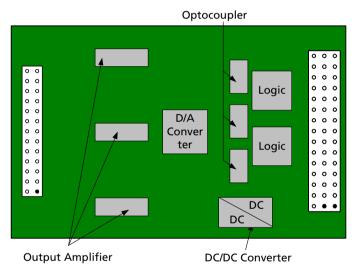

2.4.1 Signal Conditioning

The piggyback has four D/A output channels that are electrically isolated from the VMEbus system. Unipolar or bipolar conversion can be selected by solder straps. The reference voltage can be set for each channel separately. The figure shows channel A as an example of how the output stage is realized.

## Fig. 2-3 Output Circuit of the D/A Converters

The voltages of the reference output A and channel A are each generated by an output of the A/D converter.

## 2.4.2 Output Voltage Range

In unipolar mode, the output voltage of each output is 0 V to +10 V.

In bipolar mode, the voltage is -10 V to +10 V.

The unipolar or bipolar mode can be set separately for each output.

2.4.3 Digital/Analog Converter

The digital/analog converter features a 12-bit resolution while the serial data transfer time is 4  $\mu$ s per data word. The D/A converter is electrically isolated from the voltage supply of the VMEbus system.

## 2.4.4 Control Interface

The control interface of the PB1650DAC piggyback consists of two shift registers and PAL logic. It controls the 16-bit parallel/serial conversion and the data flow to the converter.

The interface also generates clock signals and the status register enabling access to the EOS (end of shift) and EOP (end of programming) signals.

Additionally, the control interface generates the "\$EA" ID byte for the PB1650DAC1.1 piggyback. The ID byte can be used to read the equipment of the carrier board using a software program.

2.4.5 Size of the Address Range

The size of the address range occupied by the PB1650DAC1.1 in your system is 256 bytes.

The B16 jumper on the ES1650.1 carrier board has to be open for this address range size.

# 2.5 Configuration

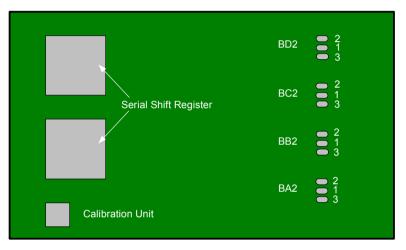

The PB1650DAC1.1 piggyback has four groups of solder straps on the solder side, one group for each output channel. They are used to select the unipolar or bipolar mode for the output voltage.

The position of each solder strap is shown in the following figure.

## Fig. 2-4 Solder Side of the PB1650DAC1.1

The table provides you with an overview of the available functions and the corresponding position of the solder straps.

| Channel | Solder Strap | Position                   | Function                                               |

|---------|--------------|----------------------------|--------------------------------------------------------|

| A       | BA2          | 1, 2 closed<br>1, 3 closed | Unipolar mode<br>Bipolar mode<br>(default setting: ds) |

| В       | BB2          | 1, 2 closed<br>1, 3 closed | Unipolar mode<br>Bipolar mode (ds)                     |

| С       | BC2          | 1, 2 closed<br>1, 3 closed | Unipolar mode<br>Bipolar mode (ds)                     |

| D       | BD2          | 1, 2 closed<br>1, 3 closed | Unipolar mode<br>Bipolar mode (ds)                     |

**Tab. 2-1**Output voltage range of the PB1650DAC1.1

## 2.6 Pin Assignment

The pin assignment of the X1 front connector of the ES1650.1 Piggyback Carrier Board depends on whether the piggyback is mounted in position A (top) or in position B (bottom).

The following two tables explain each of the two possible pin layouts.

The first letter of the signal name indicates one of the four channels A, B, C or D. "OUT" designates the signal pin of the channel and "GND" the associated ground pin.

| Signal                       | X1 Pin | Signal            | X1 Pin |

|------------------------------|--------|-------------------|--------|

| AOUT                         | 14     | AGND              | 30     |

|                              |        | AGND              | 47     |

| BOUT                         | 29     | BGND              | 13     |

|                              |        | BGND              | 45     |

| COUT                         | 44     | CGND              | 11     |

|                              |        | CGND              | 28     |

| DOUT                         | 10     | DGND              | 26     |

|                              |        | DGND              | 43     |

| Ext. reset<br>supply voltage | 9      | Ext. reset<br>GND | 42     |

| Open                         | 12     | Open              | 32     |

| Open                         | 15     | Open              | 33     |

| Open                         | 16     | Open              | 46     |

| Open                         | 17     | Open              | 48     |

| Open                         | 27     | Open              | 49     |

| Open                         | 31     | Open              | 50     |

Tab. 2-2

Pin Assignment of the PB1650DAC1.1 - Piggyback in Position A

| Signal | X1 Pin | Signal | X1 Pin |

|--------|--------|--------|--------|

| AOUT   | 38     | AGND   | 5      |

|        |        | AGND   | 22     |

| BOUT   | 4      | BGND   | 20     |

|        |        | BGND   | 37     |

| COUT   | 19     | CGND   | 3      |

Tab. 2-3

Pin Assignment of the PB1650DAC1.1 - Piggyback in Position B

| Signal | X1 Pin | Signal | X1 Pin |

|--------|--------|--------|--------|

|        |        | CGND   | 35     |

| DOUT   | 34     | DGND   | 1      |

|        |        | DGND   | 18     |

| Open   | 2      | Open   | 24     |

| Open   | 6      | Open   | 25     |

| Open   | 7      | Open   | 36     |

| Open   | 8      | Open   | 39     |

| Open   | 21     | Open   | 40     |

| Open   | 23     | Open   | 41     |

Tab. 2-3

Pin Assignment of the PB1650DAC1.1 - Piggyback in Position B

# 2.7 Technical Data

This sections contains the technical data of the PB1650DAC1.1 digital/analog converter piggyback in tabular form.

#### D/A Converter

| Resolution                | 12-bit                      |

|---------------------------|-----------------------------|

| Serial data transfer time | 4 µs per data word          |

| Rise time                 | 0.4 V per µsec              |

| Linearity error           | ±0.75 LSB                   |

| Differential linearity    | ±0.9 LSB                    |

| Туре                      | AD 7568 from Analog Devices |

## Analog Output

Output voltage in unipolar 0 V to +10 V for each output selected by solder straps mode

| Output voltage in bipolar | -10 V to +10 V for each output selected by solder |

|---------------------------|---------------------------------------------------|

| mode                      | straps                                            |

| Output current            | Max. 2 mA per channel                             |

## Power Supply

| Piggyback | +5 V DC, ±5 %, max. 290 mA |

|-----------|----------------------------|

## Environmental Conditions

| Ambient temperature during operation | 0 °C to +70 °C             |

|--------------------------------------|----------------------------|

| Storage temperature                  | -55 °C to +85 °C           |

| Relative humidity                    | 5 to 95 %, no condensation |

# 3 PB1650DIO1.1 Digital I/O Piggyback (8/8 Channels)

This section contains information about the basic features and applications of the PB1650DIO1.1 digital I/O piggyback. A block diagram shows the schematic layout of the module.

#### note

Some components of the piggyback may be damaged or destroyed by electrostatic discharges. Please keep the piggyback in its storage package until it is installed.

The piggyback should only be taken from its storage package, configured and installed at a work place that is protected against static discharge.

#### note

The components, connectors, a nd printed lines of the piggyback may carry dangerous high voltages.

These voltages may even exist when the piggyback is not installed in the VME system or when the VME system is powered off.

Make sure that the piggyback is protected against contact during its operation. Disconnect all connections to the ES1650.1 Piggyback Carrier Board before removing the board from the VME system.

#### 3.1 Features

The PB1650DIO1.1 piggyback is intended for digital input and output of switching states via eight input and eight output ports that are electrically isolated.

The piggyback provides the following features:

- eight parallel, electrically isolated digital input channels (max. 80 V DC)

- eight parallel, electrically isolated digital output channels (max. 500 mA)

- its own ID byte

#### 3.2 Applications

The PB1650DIO1.1 piggyback is used in conjunction with the ES1650.1 Piggyback Carrier Board in VMEbus systems for capturing and generating binary switching signals.

Examples of applications are:

- acquisition of output states of the ECU (energizing solenoids, reversing light relays)

- switch simulation (hand brake switch)

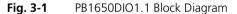

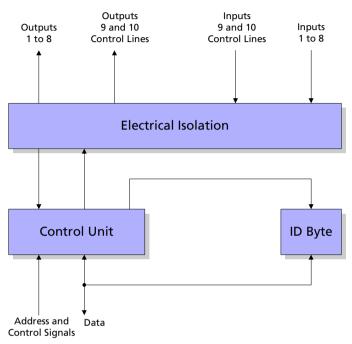

## 3.3 Block Diagram

The block diagram below illustrates the working principle of the PB1650DIO1.1 piggyback.

In the top center, you can see the electrical isolation separating the 16 input and output channels from each other and from the VMEbus system. Below it, you find the module-internal control unit. This controls the digital inputs and outputs and generates the ID byte of the piggyback.

# 3.4 PB1650DIO1.1 Hardware

This section gives you a detailed overview of the features of the PB1650DIO1.1 piggyback. You will find information on the following subjects:

- inputs

- outputs

- power ON state

- control interface

- size of the address range

The following figure shows the position of the components on the piggyback.

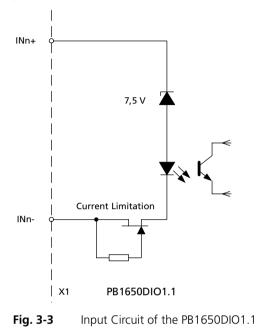

#### 3.4.1 Inputs

The input area consists of one opto-isolated input with current limitation and one input buffer to the ES1650.1 interface. There are eight parallel input channels in groups of two channels sharing one common ground per group. The input voltage range is a max. of 80 V DC.

The input current is limited to 5 mA. The input circuit does not invert.

Input levels <5 V are interpreted as a logical 0, and input levels >10 V as a logical 1. In the range from 5 V to 10 V, the switching state is undefined.

The channels 1 and 2, 3 and 4, 5 and 6, 7 and 8 each share a common ground port.

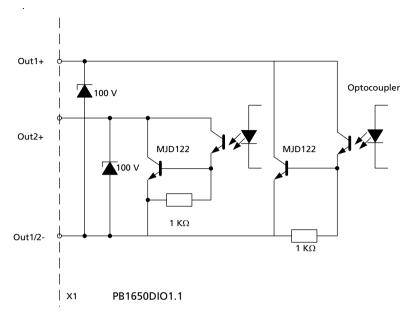

#### 3.4.2 Outputs

The output driver consists of a bipolar transistor switch, an optocoupler, and a safety diode. There are eight parallel, electrically isolated output channels in groups of two channels sharing one common ground per group.

The maximum output current per channel may not exceed 500 mA. The output voltage must be between +5 V and +80 V. Each channel can be programmed individually.

Fig. 3-4 Output Circuit of the PB1650DIO1.1

3.4.3 Power ON State

The output drivers are disabled in the power ON state and after a local reset. This means there is *no* output current.

The outputs are also disabled when the power supply of the VME system is off.

3.4.4 Control Interface

The control interface generates an ID byte for the piggyback.

The ID byte for the PB1650DIO1.1 piggyback is "\$EF". The ID byte can be used to detect the equipment of the carrier board using a software program.

3.4.5 Size of the Address Range

The size of the address range occupied by the PB1650DIO1.1 in your system is 256 bytes.

The B16 jumper on the ES1650.1 Piggyback Carrier Board has to be open for this address range size.

## 3.5 Configuration

The PB1650DIO1.1 piggyback has *no* jumpers or solder straps that need to be configured.

## 3.6 Pin Assignment

The pin assignment of the ES1650.1 Piggyback Carrier Board depends on whether the piggyback is mounted in position A (top) or in position B (bottom).

The pin assignment for each position of the piggyback is shown in a table.

"IN" means input channel, and "OUT" stands for output channel. The numbers indicate the channel number. "+" indicates the signal output of the channel; "-" the ground port of the channel. Note that every two channels share a common ground.

| Signal                       | X1 Pin | Signal            | X1 Pin |

|------------------------------|--------|-------------------|--------|

| OUT1+                        | 17     | IN1+              | 50     |

| OUT2+                        | 49     | IN2+              | 33     |

| OUT3+                        | 15     | IN3+              | 48     |

| OUT4+                        | 47     | IN4+              | 31     |

| OUT5+                        | 13     | IN5+              | 46     |

| OUT6+                        | 45     | IN6+              | 29     |

| OUT7+                        | 11     | IN7+              | 44     |

| OUT8+                        | 43     | IN8+              | 27     |

| OUT1/2-                      | 32     | IN1/2-            | 16     |

| OUT3/4-                      | 30     | IN3/4-            | 14     |

| OUT5/6-                      | 28     | IN5/6-            | 12     |

| OUT7/8-                      | 26     | IN7/8-            | 10     |

| Ext. reset<br>supply voltage | 9      | Ext. reset<br>GND | 42     |

Tab. 3-1Pin Assignment of the PB1650DIO1.1 - Piggyback in Position A<br/>(Top)

| Signal  | X1 Pin | Signal | X1 Pin |

|---------|--------|--------|--------|

| OUT1+   | 41     | IN1+   | 25     |

| OUT2+   | 24     | IN2+   | 8      |

| OUT3+   | 39     | IN3+   | 23     |

| OUT4+   | 22     | IN4+   | 6      |

| OUT5+   | 37     | IN5+   | 21     |

| OUT6+   | 20     | IN6+   | 4      |

| OUT7+   | 35     | IN7+   | 19     |

| OUT8+   | 18     | IN8+   | 2      |

| OUT5/6- | 3      | IN1/2- | 40     |

| OUT3/4- | 5      | IN3/4- | 38     |

| OUT1/2- | 7      | IN5/6- | 36     |

| OUT7/8- | 1      | IN7/8- | 34     |

Tab. 3-2Pin Assignment of the PB1650DIO1.1 - Piggyback in Position B<br/>(Bottom)

# 3.7 Technical Data

This section contains the technical data of the PB1650DIO1.1 piggyback in tabular form.

Digital Inputs

| Input channels  | Eight, opto-isolated, every two channels having one common ground |

|-----------------|-------------------------------------------------------------------|

| Input voltage   | 12 to 80 V DC                                                     |

| Switching level | <5 V = low<br>>10 V = high                                        |

| Input current   | 5 mA across the entire input voltage range                        |

# Digital Outputs

| Output channels                                     | Eight, opto-isolated, every two channels having one common ground |

|-----------------------------------------------------|-------------------------------------------------------------------|

| Output voltage                                      | 0 to 80 V DC                                                      |

| Supply voltage for exter-<br>nal pull-up resistance | 5 to 80 V DC                                                      |

| Output current                                      | 500 mA max.                                                       |

# Channel Properties

| Input frequency   | 6.5 kHz max.                                                                        |

|-------------------|-------------------------------------------------------------------------------------|

| Isolation voltage | 2500 V RMS between input and digital ground of<br>VMEbus<br>100 V DC between inputs |

# Environmental Conditions

| Ambient temperature during operation | 0 to +70 °C                |

|--------------------------------------|----------------------------|

| Storage temperature                  | -55 to +85 °C              |

| Relative humidity                    | 0 to 95% (no condensation) |

# Physical Dimensions

| Length | 100 mm |

|--------|--------|

| Width  | 48 mm  |

| Depth  | 12 mm  |

# 4 PB1650DIO2.1 Digital I/O Piggyback (10/10 Channels)

This section contains information about the basic features and applications of the PB1650DIO2.1 digital I/O piggyback. A block diagram shows the schematic layout of the module.

#### note

Some components of the piggyback may be damaged or destroyed by electrostatic discharges. Please keep the piggyback in its storage package until it is installed.

The piggyback should only be taken from its storage package, configured and installed at a work place that is protected against static discharge.

### 4.1 Features

The PB1650DIO2.1 piggyback is used for the digital input and output of switching states via eight input and eight output ports which are dc decoupled.

The piggyback provides the following features:

- eight parallel, dc decoupled, digital input channels

- eight parallel, dc decoupled, digital output channels

- four parallel, dc decoupled, control lines

- its own ID byte

### 4.2 Applications

The PB1650DIO2.1 piggyback is used in conjunction with the ES1650.1 Piggyback Carrier Board in VMEbus systems for capturing and generating binary switching signals with TTL signal levels.

Examples of applications are:

- acquisition of switching outputs of the ECU (energizing solenoids, reversing light relays)

- switch simulation

## 4.3 Block Diagram

The block diagram below illustrates the working principle of the PB1650DIO2.1 piggyback.

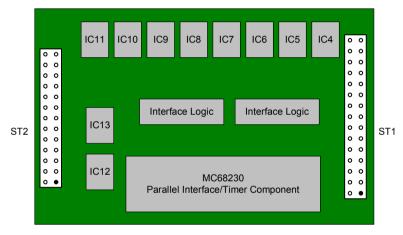

#### ES1650.1

In the top center, you can see the dc decoupling electrically separating the 16 input and output channels and the four control lines from the VMEbus system. Below it, you find the module-internal control unit. This controls the digital inputs and outputs and generates the ID byte of the piggyback.

# 4.4 PB1650DIO2.1 Hardware

This section gives you a detailed overview of the features of the PB1650DIO2.1 piggyback. You will find information on the following subjects:

- inputs

- outputs

- power ON state

- control interface

- size of the address range

The following figure shows the position of the components on the piggyback.

IC4-IC13: Optocouplers

Fig. 4-2 Component Side of the PB1650DIO2.1

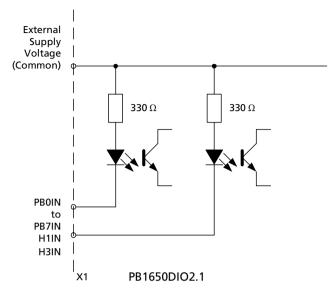

4.4.1 Inputs

The input area consists of one dc decoupled input and one input buffer to the ES1650.1 interface. There are eight parallel input channels and two parallel control lines. The two control lines, H1E and H3E, can either be configured as inputs or as control lines. The input voltage range is 0 to 5 V DC.

The following figure shows the allocation of an input channel.

The input current must not exceed 10 mA. The input circuit does not invert.

Input levels <1.5 V are interpreted as a logical 0 (low), and input levels >3.0 V as a logical 1 (high). The switching state is undefined in the range 1.5 V to 3.0 V.

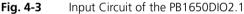

## 4.4.2 Outputs

The output drivers consist of a bipolar transistor switch and an optocoupler. There are eight parallel, dc decoupled output channels and two parallel control lines, H2E and H4E, which can be configured as outputs.

The following figure shows the allocation of an output channel.

Fig. 4-4 Output Circuit of the PB1650DIO2.1

The maximum output current per channel must not exceed 10 mA. The outputs have a pull-up resistance of 10 k $\Omega$ .

All output and input channels have a common ground and supply voltage (VCC) which has to be applied from outside.

4.4.3 Power ON State

The output drivers are disabled in the power ON state and after a local reset. This means there is *no* output current.

The outputs are also disabled when the power supply of the VMEbus system is off.

### 4.4.4 Control Interface

The control interface generates an ID byte for the piggyback.

The ID byte for the PB1560DIO2.1 piggyback is "\$F2". The ID byte can be used to detect the equipment of the carrier board using a software program.

### 4.4.5 Size of the Address Range

The size of the address range occupied by the PB1650DIO2.1 in your system is 256 bytes.

The B16 jumper on the ES1650.1 Piggyback Carrier Board has to be open for this address range size.

## 4.5 Configuration

The PB1650DIO2.1 piggyback has *no* jumpers or solder straps that need to be configured.

## 4.6 Pin Assignment

The pin assignment of the 50-pin front-facing connector of the ES1650.1 Piggyback Carrier Board depends on whether the piggyback is mounted in position A (top) or in position B (bottom).

The pin assignment for each position of the piggyback is shown in a table.

"IN" means input channel, and "OUT" stands for output channel. The numbers indicate the channel number. "H" means handshake line.

| Signal                       | X1 Pin | Signal            | X1 Pin |

|------------------------------|--------|-------------------|--------|

| PA0 OUT                      | 33     | PAO IN            | 49     |

| PA1 OUT                      | 16     | PA1 IN            | 32     |

| PA2 OUT                      | 48     | PA2 IN            | 15     |

| PA3 OUT                      | 31     | PA3 IN            | 47     |

| PA4 OUT                      | 14     | PA4 IN            | 30     |

| PA5 OUT                      | 46     | PA5 IN            | 13     |

| PA6 OUT                      | 29     | PA6 IN            | 45     |

| PA7 OUT                      | 12     | PA7 IN            | 28     |

| H2E OUT                      | 27     | H1E IN            | 44     |

| H4E OUT                      | 43     | H3E IN            | 11     |

| Ext. supply<br>voltage       | 50     | Ext. GND          | 10     |

|                              |        | Ext. GND          | 17     |

|                              |        | Ext. GND          | 26     |

| Ext. reset<br>supply voltage | 9      | Ext. reset<br>GND | 42     |

Tab. 4-1Pin Assignment of the PB1650DIO2.1 - Piggyback in Position A<br/>(Top)

| Signal                       | X1 Pin | Signal            | X1 Pin |

|------------------------------|--------|-------------------|--------|

| PB0 OUT                      | 8      | PBO IN            | 24     |

| PB1 OUT                      | 40     | PB1 IN            | 7      |

| PB2 OUT                      | 23     | PB2 IN            | 39     |

| PB3 OUT                      | 6      | PB3 IN            | 22     |

| PB4 OUT                      | 38     | PB4 IN            | 5      |

| PB5 OUT                      | 21     | PB5 IN            | 37     |

| PB6 OUT                      | 4      | PB6 IN            | 20     |

| PB7 OUT                      | 36     | PB7 IN            | 3      |

| H2E OUT                      | 2      | H1E IN            | 19     |

| H4E OUT                      | 18     | H3E IN            | 35     |

| Ext. supply<br>voltage       | 25     | Ext. GND          | 1      |

|                              |        | Ext. GND          | 34     |

|                              |        | Ext. GND          | 41     |

| Ext. reset<br>supply voltage | 9      | Ext. reset<br>GND | 42     |

Tab. 4-2Pin Assignment of the PB1650DIO2.1 - Piggyback in Position B<br/>(Bottom)

# 4.7 Technical Data

This section contains the technical data of the PB1650DIO2.1 piggyback in tabular form.

# Digital Inputs

| Input channels  | Eight, dc decoupled, two control lines, opto-isolated |

|-----------------|-------------------------------------------------------|

| Input voltage   | 5 V DC                                                |

| Switching level | <1.5 V = low<br>≥3.0 V = high                         |

| Input current   | 10 mA at 5 V                                          |

# Digital Outputs

| Output channels | Eight, dc decoupled, two control lines, opto-isolated |

|-----------------|-------------------------------------------------------|

| Output voltage  | 5 V max.                                              |

| Output current  | 10 mA max.                                            |

# Channel Properties

| Input frequency   | 500 kHz max.                                              |

|-------------------|-----------------------------------------------------------|

| Isolation voltage | 2500 V RMS between input and digital ground of the VMEbus |

# Environmental Conditions

| Ambient temperature during operation | 0 to +70 °C                |

|--------------------------------------|----------------------------|

| Storage temperature                  | -40 to +85 °C              |

| Relative humidity                    | 0 to 95% (no condensation) |

# Physical Dimensions

| Length | 100 mm |  |

|--------|--------|--|

| Width  | 48 mm  |  |

| Depth  | 12 mm  |  |

# 5 PB1650ADC1.1 A/D Piggyback (8 Channels)

This section contains information about the basic features and applications of the PB1650ADC1.1 A/D piggyback. A block diagram shows the schematic layout of the module.

#### note

Some components of the piggyback may be damaged or destroyed by electrostatic discharges. Please keep the piggyback in its storage package until it is installed.

The piggyback should only be taken from its storage package, configured and installed at a work place that is protected against static discharge.

### 5.1 Features

The PB1650ADC1.1 piggyback is used for analog data acquisition in VMEbus systems in conjunction with the ES1650.1 Piggyback Carrier Board. The module is designed for medium resolutions and small to medium data rates. It has the following features:

- analog/digital conversion with 12-bit resolution and a max. sampling rate of 20 kHz

- 8 unipolar or bipolar input channels, programmed by software

- four input voltage ranges

- ID byte

### 5.2 Applications

The PB1650ADC1.1 piggyback can be used in VMEbus systems where analog input signals need to be acquired.

Examples of applications are:

- acquisition of analog sensor signals, such as engine temperature, oil temperature, accelerator position

- acquisition of analog output variables of the ECU, such as PMW signals

- simulation of analog sensors receiving a control or reference voltage from the ECU

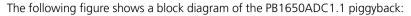

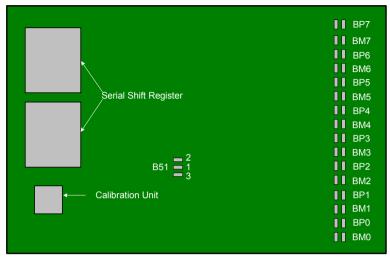

# 5.3 Block Diagram

At the top of the diagram, you can see the eight analog inputs, and, moving down, the signal conditioner and the analog/digital converter. The signals pass to the shift register via optocouplers (i.e. fully electrically isolated) and from there to the VMEbus interface of the basic board. The control logic is part of the piggyback. It controls the converters and shift registers, passing the data to the ES1650.1 Piggyback Carrier Board.

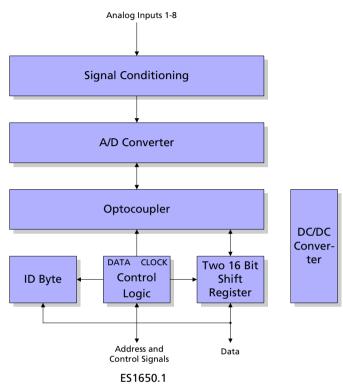

# 5.4 PB1650ADC1.1 Hardware

This section gives you a detailed overview of the features of the PB1650ADC1.1 piggyback. The following subjects are explained:

- signal conditioning

- input voltage range and gain

- analog/digital converter

- control interface

- ID byte

- size of the address range

The following figure shows the position of the components on the piggyback.

### 5.4.1 Signal Conditioning

The board has eight analog unipolar (single-ended) or bipolar inputs. Each channel has its own preamplifier.

The mode (unipolar or bipolar) can be selected for each channel using the software.

### 5.4.2 Input Voltage Range and Gain

The input voltage in unipolar mode is 0 V to +5 V or 0 V to +10 V. The input voltage in bipolar mode is -5 V to +5 V or -10 V to +10 V.

The input amplifier gain can be set to 0.4975 or 0.9901 for each channel using jumpers.

### 5.4.3 A/D Converter

The analog/digital converter features a 12-bit resolution and a max. sampling rate of 20 kHz. The conversion delay is 43  $\mu$ sec.

The converter applies the successive approximation method requiring four clock cycles for each of the twelve approximation steps.

### 5.4.4 Control Logic

The control logic, in conjunction with the two shift registers, forms the serial interface to the A/D converter and the associated calibration component.

It also forms the status register, thus controlling the conversion time.

### 5.4.5 ID Byte

The control interface also generates an ID byte for the piggyback. The ID byte for the PB1650ADC1.1 piggyback is \$F4. The ID byte can be used to detect the equipment of the ES1650.1 Piggyback Carrier Board using a software program.

#### 5.4.6 Size of the Address Range

The size of the address range occupied by the PB1650ADC1.1 in your system is 256 bytes.

The B16 jumper on the ES1650.1 Piggyback Carrier Board has to be open for this address range size.

### 5.5 Configuration

This section contains the information for configuring the solder straps of the PB1650ADC1.1 piggyback. The following configurations can be set using solder straps:

- input voltage range

- offset voltage

The figure below shows the position of the solder straps on the solder side of the board.

Fig. 5-3 PB1650ADC1.1 Solder Side with Solder Straps

# 5.5.1 Input Voltage Range

The following table describes the function of each solder strap.

| Input Channel | Solder Strap | Position       | Input Voltage Range                    |

|---------------|--------------|----------------|----------------------------------------|

| 0             | BPO, BMO     | Open<br>Closed | 0-10 V and +/-10 V<br>0-5 V and +/-5 V |

| 1             | BP1, BM1     | Open<br>Closed | 0-10 V and +/-10 V<br>0-5 V and +/-5 V |

| 2             | BP2, BM2     | Open<br>Closed | 0-10 V and +/-10 V<br>0-5 V and +/-5 V |

| 3             | ВРЗ, ВМЗ     | Open<br>Closed | 0-10 V and +/-10 V<br>0-5 V and +/-5 V |

| 4             | BP4, BM4     | Open<br>Closed | 0-10 V and +/-10 V<br>0-5 V and +/-5 V |

Tab. 5-1

Input Voltage Range of the PB1650ADC1.1

| Input Channel | Solder Strap | Position       | Input Voltage Range                    |

|---------------|--------------|----------------|----------------------------------------|

| 5             | BP5, BM5     | Open<br>Closed | 0-10 V and +/-10 V<br>0-5 V and +/-5 V |

| 6             | BP6, BM6     | Open<br>Closed | 0-10 V and +/-10 V<br>0-5 V and +/-5 V |

| 7             | BP7, BM7     | Open<br>Closed | 0-10 V and +/-10 V<br>0-5 V and +/-5 V |

Tab. 5-1Input Voltage Range of the PB1650ADC1.1 (cont'd)

## 5.5.2 Offset Voltage

Use jumper B51 to select the common offset voltage for all input channels.

| Solder Str | ap Position           | Input Voltage                               |

|------------|-----------------------|---------------------------------------------|

| B51        | 1-3 closed            | No additional offset voltage at each input  |

| B51        | 1-2 closed            | Approx. 7.5 mV offset voltage at each input |

| Tab E 2    | Offcot Valtage of the |                                             |

Tab. 5-2Offset Voltage of the PB1650ADC1.1

## 5.6 Pin Assignment

The pin assignment of the X1 front connector of the ES1650.1 Piggyback Carrier Board depends on whether the piggyback is mounted in position A (top) or in position B (bottom).

The pin assignment for each position of the piggyback is shown in a table.

"A" indicates the non-inverting and "B" the inverting input of the channel. If you want to measure a voltage, the signal has to be applied between connections A and B.

The number following the letter indicates the channel number.

| Signal | X1 Pin | Signal | X1 Pin |

|--------|--------|--------|--------|

| A0(+)  | 50     | B0(-)  | 17     |

| A1(+)  | 16     | B1(-)  | 32     |

| A2(+)  | 48     | B2(-)  | 15     |

| A3(+)  | 14     | B3(-)  | 30     |

| A4(+)  | 46     | B4(-)  | 13     |

| A5(+)  | 12     | B5(-)  | 28     |

Tab. 5-3

Pin Assignment of the PB1650ADC1.1 - Piggyback in Position A

| Signal                       | X1 Pin | Signal            | X1 Pin |

|------------------------------|--------|-------------------|--------|

| A6(+)                        | 44     | B6(-)             | 11     |

| A7(+)                        | 10     | B7(-)             | 26     |

| Ext. reset<br>supply voltage | 9      | Ext. reset<br>GND | 42     |

| Ground                       | 27     | Ground            | 43     |

| Ground                       | 29     | Ground            | 45     |

| Ground                       | 31     | Ground            | 47     |

| Ground                       | 33     | Ground            | 49     |

Tab. 5-3

Pin Assignment of the PB1650ADC1.1 - Piggyback in Position A

| Signal | X1 Pin | Signal | X1 Pin |

|--------|--------|--------|--------|

| A0(+)  | 25     | B0(-)  | 41     |

| A1(+)  | 40     | B1(-)  | 7      |

| A2(+)  | 23     | B2(-)  | 39     |

| A3(+)  | 38     | B3(-)  | 5      |

| A4(+)  | 21     | B4(-)  | 37     |

| A5(+)  | 36     | B5(-)  | 3      |

| A6(+)  | 19     | B6(-)  | 35     |

| A7(+)  | 34     | B7(-)  | 1      |

| Ground | 2      | Ground | 18     |

| Ground | 4      | Ground | 20     |

| Ground | 6      | Ground | 22     |

| Ground | 8      | Ground | 24     |

Tab. 5-4

Pin Assignment of the PB1650ADC1.1 - Piggyback in Position B

# 5.7 Technical Data

This section contains the technical data of the PB1650ADC1.1 analog/digital converter piggyback in tabular form.

Analog/Digital Converter

| Resolution       | 12-bit      |

|------------------|-------------|

| Conversion delay | 43 µs       |

| Sampling rate    | 20 kHz      |

| Linearity        | +/-0.75 LSB |

# Analog Input

| Analog channels        | 8                                                                |

|------------------------|------------------------------------------------------------------|

| Input resistance       | In the 5 V range: 20 K $\Omega$ In the 10 V range: 40 K $\Omega$ |

| Overvoltage protection | +/- 35 V continuous                                              |

| Input voltage          | Unipolar: 0 to 5 V, 0 to 10 V<br>Bipolar: +/-5 V, +/-10 V        |

# Environmental Conditions

| Ambient temperature | 0 to +70 °C |  |

|---------------------|-------------|--|

| Amperature          | 010470 C    |  |

| during operation    |             |  |

| during operation    |             |  |

# Physical Dimensions

| Length | 100 mm |

|--------|--------|

| Width  | 48 mm  |

| Depth  | 12 mm  |

# 6 PB1650REL1.1 Relay Piggyback (8 Channels)

This section contains information about the basic features and applications of the PB1650REL1.1 relay piggyback. A block diagram shows the schematic layout of the module.

#### note

Some components of the piggyback may be damaged or destroyed by electrostatic discharges. Please keep the piggyback in its storage package until it is installed.

The piggyback should only be taken from its storage package, configured and installed at a work place that is protected against static discharge.

#### note

The components, connectors, and printed lines of the piggyback may carry dangerous high voltages.

These voltages may even exist when the piggyback is not installed in the VME system or when the VME system is powered off.

Make sure that the piggyback is protected against contact during its operation. Disconnect all connections to the ES1650.1 Piggyback Carrier Board before removing the plug-in board from the VME system.

## 6.1 Features

This piggyback provides eight electrically isolated switches in the voltage range up to 175 V.

The piggyback has the following features:

- voltages up to 175 V, currents up to 250 mA

- its own ID byte

### 6.2 Applications

The PB1650REL1.1 piggyback can be used in VMEbus systems as a switch in conjunction with the ES1650.1 Piggyback Carrier Board.

Typical applications are the simulation of manual switches or the switching of loads that cannot be switched using semiconductor switches. The PB1650REL1.1 piggyback can also be used as an analog multiplexer.

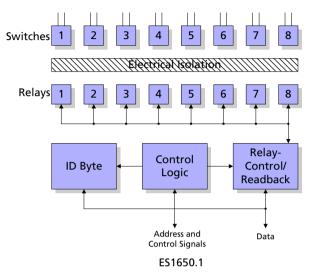

## 6.3 Block Diagram

The block diagram below illustrates the working principle of the module.

At the top, adjacent to the user side, you can see eight relay change-over switches, electrically isolated from each other and from the VMEbus system. Their switching states are detected by the logic in the bottom center. The function of the relays is controlled by a separate control interface on the module. In addition, the PB1650REL1.1 has its own ID, as can be seen on the extreme left of the block diagram. This end of the board is also where the board is connected to the VMEbus via the interface to the ES1650.1 Piggyback Carrier Board.

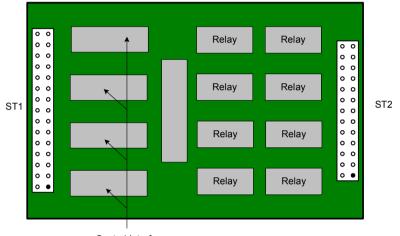

# 6.4 PB1650REL1.1 Hardware

This section gives you a detailed overview of the features of the PB1650REL1.1 piggyback. You will find information on the following subjects:

- relays

- output voltage range

- ID byte and address

- size of the address range

The following figure shows the position of the components on the component side of the piggyback.

Control Interface

- Fig. 6-2 Component Side of the PB1650REL1.1

- 6.4.1 Relays

The relay piggyback has eight relays. The contacts are electrically isolated from each other and from the VMEbus system. Each relay is equipped with a change-over switch.

6.4.2 Output Voltage Range

The relays are capable of switching up to 175 V DC and 250 mA. The maximum switching power is 3 W per contact.

### 6.4.3 ID Byte

The ID byte of the PB1650REL1.1 piggyback is "\$FC". The ID byte can be used to detect the equipment of the ES1650.1 Piggyback Carrier Board using a software program.

#### 6.4.4 Size of the Address Range

The size of the address range occupied by the PB1650REL1.1 in your system is 256 bytes.

The B16 jumper on the ES1650.1 Piggyback Carrier Board has to be open for this address range size.

### 6.5 Configuration

The PB1650REL1.1 piggyback has *no* jumpers or solder straps that need to be configured.

## 6.6 Pin Assignment

The pin assignment of the ES1650.1 Piggyback Carrier Board depends on whether the piggyback is mounted in position A (top) or in position B (bottom).

The pin assignment for each position of the piggyback is shown in a table.

Key to abbreviations:

- Pole: center contact

- NC: normally closed

- NO: normally open

The number indicates the channel number.

| Signal     | X1 Pin | Signal     | X1 Pin |

|------------|--------|------------|--------|

| Relay 0 NC | 49     | Relay 0 NO | 50     |

| Relay 1 NC | 48     | Relay 1 NO | 16     |

| Relay 2 NC | 47     | Relay 2 NO | 15     |

| Relay 3 NC | 46     | Relay 3 NO | 14     |

| Relay 4 NC | 45     | Relay 4 NO | 13     |

| Relay 5 NC | 44     | Relay 5 NO | 12     |

| Relay 6 NC | 43     | Relay 6 NO | 11     |

Tab. 6-1Pin Assignment of the PB1650REL1.1 - Piggyback in Position A<br/>(Top)

| Signal                       | X1 Pin | Signal            | X1 Pin |

|------------------------------|--------|-------------------|--------|

| Relay 7 NC                   | 17     | Relay 7 NO        | 10     |

| Relay 0 Pole                 | 33     | Relay 4 Pole      | 29     |

| Relay 1 Pole                 | 32     | Relay 5 Pole      | 28     |

| Relay 2 Pole                 | 31     | Relay 6 Pole      | 27     |

| Relay 3 Pole                 | 30     | Relay 7 Pole      | 26     |

| Ext. reset<br>supply voltage | 9      | Ext. reset<br>GND | 42     |

Tab. 6-1

Pin Assignment of the PB1650REL1.1 - Piggyback in Position A (Top) (cont'd)

| Signal       | X1 Pin | Signal       | X1 Pin |

|--------------|--------|--------------|--------|

| Relay 0 NC   | 24     | Relay 0 NO   | 25     |

| Relay 1 NC   | 23     | Relay 1 NO   | 40     |

| Relay 2 NC   | 22     | Relay 2 NO   | 39     |

| Relay 3 NC   | 21     | Relay 3 NO   | 38     |

| Relay 4 NC   | 20     | Relay 4 NO   | 37     |

| Relay 5 NC   | 19     | Relay 5 NO   | 36     |

| Relay 6 NC   | 18     | Relay 6 NO   | 35     |

| Relay 7 NC   | 41     | Relay 7 NO   | 34     |

| Relay 0 Pole | 8      | Relay 4 Pole | 4      |

| Relay 1 Pole | 7      | Relay 5 Pole | 3      |

| Relay 2 Pole | 6      | Relay 6 Pole | 2      |

| Relay 3 Pole | 5      | Relay 7 Pole | 1      |

Tab. 6-2Pin Assignment of the PB1650REL1.1 - Piggyback in Position B<br/>(Bottom)

# 6.7 Technical Data

This section contains the technical data of the PB1650REL1.1 piggyback in tabular form.

# Outputs

| Number of<br>output channels | 8 (electrically isolated) |

|------------------------------|---------------------------|

| Switching voltage            | Max. 175 V DC             |

| Switching current            | Max. 250 mA               |

| Switching power              | Max. 3 W per relay        |

| Switching time               | < 3 msec                  |

# Power Supply

| Supply voltage | +5 V (±5 %)                            |

|----------------|----------------------------------------|

| Supply current | 100 mA + 22.5 mA per activated channel |

# Environmental Conditions

| Ambient temperature during operation | 0 to +70 °C               |

|--------------------------------------|---------------------------|

| Storage temperature                  | -55 to +85 °C             |

| Relative humidity                    | 0 to 95 % no condensation |

# Physical Dimensions

| Length | 100 mm |  |

|--------|--------|--|

| Width  | 48 mm  |  |

| Depth  | 12 mm  |  |

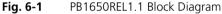

# 7 PB1650PRT1.1 Prototyping Piggyback

This section contains information about the basic features and applications of the PB1650PRT1.1 Prototyping Piggyback. A block diagram shows the schematic layout of the module.

#### note

Some components of the piggyback may be damaged or destroyed by electrostatic discharges. Please keep the piggyback in its storage package until it is installed.

The piggyback should only be taken from its storage package, configured and installed at a work place that is protected against static discharge.

## 7.1 Features

The PB1650PRT1.1 Prototyping Piggyback is used for constructing circuits in a wrap area. You can mount the ES4060.1 processor module on the prototyping piggyback to execute universal control tasks.

The piggyback has the following features:

• wrap area that can be equipped individually to suit your applications

The following functions are also available to you in conjunction with the optional ES4060.1 processor module:

- serial FLASH memory

- Dual-Ported RAM for data transfer from and to the VMEbus

#### note

The PB1650PRT1.1 Prototyping Piggyback takes up both slots for piggybacks on the ES1650.1 Piggyback Carrier Board.

## 7.2 Applications

The PB1650PRT1.1 Prototyping Piggyback is used in conjunction with the ES1650.1 Piggyback Carrier Board in VMEbus systems to develop various circuits.

Examples of application areas are:

- with ES4060.1 processor module: development of complex microprocessor-based control and data acquisition circuits which use analog, digital or PWM inputs and outputs, a VMEbus or a CANbus interface

- without ES4060.1 processor module: development of circuits for signal conditioning

The PB1650PRT1.1 Prototyping Piggyback is normally used with the ES4060.1 Processor Module. The processor module makes a range of I/O, PWM and A/D channels, and various interfaces such as SPI, CAN, JTAG etc. available. These can be addressed using the VMEbus or CAN interface. For more information on programming the interfaces and peripheral units as well as on data exchange using the VMEbus and the CAN interface, please refer to the firmware manual on the ES4060.1 Processor Module.

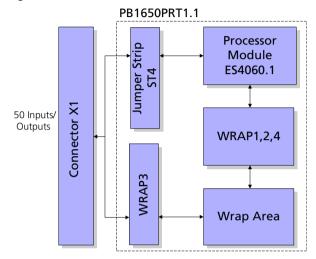

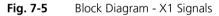

The block diagram below illustrates the working principle of the PB1650PRT1.1 Piggyback.

ES1650.1

#### Fig. 7-1 PB1650PRT1.1 Block Diagram

At the top of the diagram you can see the X1 connector and the inputs and outputs of the ES1650.1 Piggyback Carrier Board. If you develop circuits with the ES4060.1 Processor Module, the signals are transferred to the VMEbus interface on the carrier board via the processor module and the Dual-Ported RAM (DPRAM).

Configuration data for the processor module and user-specific data are stored in the Flash memory.

The wrap area is available for constructing individual circuits.

Both the wrap area and the ES4060.1 Processor Module have common connections to the carrier board's front-facing connector, X1.

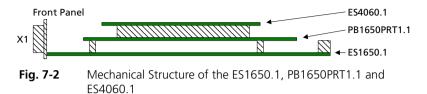

The figure below shows a side view of the mechanical structure of the three circuits on the board.

# 7.3 PB1650PRT1.1 Hardware

This section gives you a detailed overview of the features of the PB1650PRT1.1 Prototyping Piggyback. You will find information on the following subjects:

- supply voltages

- interfaces

- Dual-Ported RAM access

- size of the address range

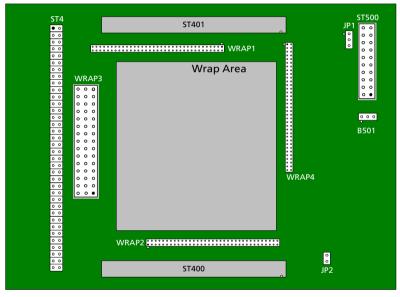

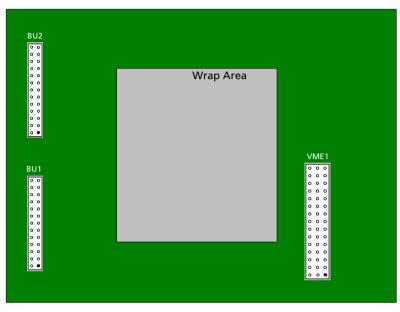

The following figure shows the position of the components on the component side of the prototyping piggyback.

Fig. 7-3 Component Side of the PB1650PRT1.1

Fig. 7-4 Solder Side of the PB1650PRT1.1

7.3.1 Supply Voltages

The prototyping module makes supply voltages of +3.3 V and +5 V available. The voltages are available at pins on the wrap area and at the X1 connector on the front panel of the ES1650.1 Piggyback Carrier Board.

#### note

The supply voltages are **not** protected against short-circuits and overvoltage. Short-circuits on the wrap area or on the front-facing connector can damage the PB1650PRT1.1, the ES1650.1 Piggyback Carrier Board and the ES4060.1 Processor Module.

To avoid damage to the components, make sure that the circuits on the prototyping module are wired correctly before switching on the supply voltage.

### 7.3.2 VMEbus Interface

There is direct access to the 4-KByte Dual-Ported RAM area via the VMEbus interface. The address range within the VMEbus address range is determined by the configuration of the base address of the ES1650.1 Piggyback Carrier Board.

### 7.3.3 Dual-Ported RAM Access

The data is transferred between the VMEbus and the PB1650PRT1.1 module using a 2048 K x 16-bit Dual-Ported RAM memory.

Only 16-bit VMEbus accesses to the DPRAM are possible.

Only 32-bit accesses are admissible from the MPC555 to the 16-bit DPRAM due to the different data bus access modes of MPC555 and VMEbus with 8-bit, 16-bit and 32-bit accesses and an inconsistent connection of the 16-bit Dual-Ported RAM component. The most significant 16 bits have an undefined value in read operations and have to be masked out (e.g. with a logical 'AND' with 0x0000FFFF). The relevant 16-bit words are on the VMEbus, which can only make 16-bit accesses to the DPRAM, each at an interval of 32 bits, i.e. only to even DPRAM addresses.

| DPRAM Address | MPC555 32-Bit Access | VME 16-Bit Access |

|---------------|----------------------|-------------------|

| 0             | Byte 0               | Byte O            |

| 1             | Byte 1               | Byte 1            |

| 2             | Undef.               | Undef.            |

| 3             | Undef.               | Undef.            |

| 4             | Byte 2               | Byte 2            |

| 5             | Byte 3               | Byte 3            |

| 6             | Undef.               | Undef.            |

| 7             | Undef.               | Undef.            |

|               |                      |                   |

A standard storage interface from the VMEbus and MPC555 can be realized by using C macros for 8-bit, 16-bit and 32-bit accesses.

The two examples below are two C macros for the 16-bit read and write access of the MPC555 to the DPRAM. Only a slight adaptation is necessary for accessing even addresses. When accessing odd addresses, there has to be a division into bytes:

```

#define DPR W16B(Adr, Dat) {\

if ((Adr) & 0x1) {\

*(volatile uint32*)(DPRam Adr+\

(((Adr)-1) << 1)) = (((Dat) & 0xFF00) >> 8) |

(*(volatile uint32*)(DPRam Adr+\

(((Adr)-1)<<1)) & 0xFF00); \

* (volatile uint32*) (DPRam Adr+\

(((Adr)+1)<<1) = (((Dat) \overline{\&} 0xFF) <<8) |

(*(volatile uint32*)(SPRam Adr+\

(((Adr)+1)<<1)) & OxFF);\

}\

else

* (volatile uint32*) (DPRam Adr+\

((Adr) <<1)) = Dat; \

}

#define DPR R16B(Adr) ((Adr) & 0x1) ?\

((*(volatile uint32*)(DPRam Adr+(((Adr)-1)<<1)) &\

0x00FF) << 8)+\

((*(volatile uint32*)(DPRam Adr+(((Adr)+1)<<1)) &\

0xFF00) >> 8); :\

*(volatile uint32*)(DPRam Adr+((Adr)<<1)) & 0xFFFF

```

### 7.3.4 Size of the Address Range

The size of the address range occupied by the PB1650PRT1.1 in your system is 8 KBytes.

The B16 jumper on the ES1650.1 Piggyback Carrier Board has to be closed for this address range size.

### 7.4 Configuration

This section contains information on configuring the jumpers of the PB1650PRT1.1 Piggyback.

The jumpers are used to configure the hardware of the PB1650PRT1.1 module.

### 7.4.1 B501 Jumper

The write protection of the serial Flash memory is configured with jumper B501.

| B501 Jumper      | Means                                                                                                      |

|------------------|------------------------------------------------------------------------------------------------------------|

| Pin 1-2 closed   | Programming of the serial Flash memory with the ES4060.1 Processor Module or via the programming interface |

| Pin 3-2 closed   | Programming of the serial Flash memory only via the programming interface                                  |

| Tab 7 1 DEO1 lur |                                                                                                            |

Tab. 7-1

B501 Jumper

The default setting for Pins 1-2 is closed.

### 7.4.2 JP1 Jumper

Jumper JP1 determines the speed of the DPRAM access from the VMEbus.

| JP1 Jumper     | Means             |

|----------------|-------------------|

| Pin 1-2 closed | 65 ns acknowledge |

| Pin 3-2 closed | 35 ns acknowledge |

|                |                   |

Tab. 7-2JP1 Jumper

The default setting for Pins 3-2 is closed.

### 7.4.3 JP2 Jumper

The JP2 jumper configures the JTAG chain. If JTAG components are used on the wrap area, the JTAG chain can be opened to make the integration of these components in the configuration of the default JTAG chain possible. The JTAG signals are made available via the WRAP connector.