# RTA-OS ZynqUSA53/ARM Port Guide

# Copyright

The data in this document may not be altered or amended without special notification from ETAS GmbH. ETAS GmbH undertakes no further obligation in relation to this document. The software described in it can only be used if the customer is in possession of a general license agreement or single license. Using and copying is only allowed in concurrence with the specifications stipulated in the contract. Under no circumstances may any part of this document be copied, reproduced, transmitted, stored in a retrieval system or translated into another language without the express written permission of ETAS GmbH.

©Copyright 2008-2018 ETAS GmbH, Stuttgart.

The names and designations used in this document are trademarks or brands belonging to the respective owners.

Document: 10721-PG-5.0.1 EN-10-2018

# 2 Copyright

# **Safety Notice**

This ETAS product fulfills standard quality management requirements. If requirements of specific safety standards (e.g. IEC 61508, ISO 26262) need to be fulfilled, these requirements must be explicitly defined and ordered by the customer. Before use of the product, customer must verify the compliance with specific safety standards.

# Contents

| 1 | Introduc<br>1.1 |            |                                        | <b>7</b><br>8 |

|---|-----------------|------------|----------------------------------------|---------------|

|   | 1.2             |            | t Conventions                          | 8             |

|   | 1.3             |            | es                                     | 9             |

| 2 | Installin       | g the RTA  | A-OS Port Plug-in                      | 10            |

|   | 2.1             | Preparing  | to Install                             | 10            |

|   |                 | 2.1.1      | Hardware Requirements                  | 10            |

|   |                 | 2.1.2      | Software Requirements                  | 10            |

|   | 2.2             |            | on                                     | 11            |

|   |                 | 2.2.1      | Installation Directory                 | 11            |

|   | 2.3             | -          |                                        | 12            |

|   |                 | 2.3.1      | Installing the ETAS License Manager    | 12            |

|   |                 | 2.3.2      | Licenses                               | 13            |

|   |                 | 2.3.3      | Installing a Concurrent License Server | 14            |

|   |                 | 2.3.4      | Using the ETAS License Manager         | 15            |

|   |                 | 2.3.5      | Troubleshooting Licenses               | 18            |

| 3 |                 |            | stallation                             | 21            |

|   | 3.1             | -          | the Port                               | 21            |

|   | 3.2             | Running    | the Sample Applications                | 21            |

| 4 | Port Cha        | aracterist | ics                                    | 23            |

|   | 4.1             |            | ers of Implementation                  | 23            |

|   | 4.2             | •          | ation Parameters                       | 23            |

|   |                 | 4.2.1      | Stack used for C-startup               | 23            |

|   |                 | 4.2.2      | Stack used when idle                   | 24            |

|   |                 | 4.2.3      | Stack overheads for ISR activation     | 24            |

|   |                 | 4.2.4      | Stack overheads for ECC tasks          | 24            |

|   |                 | 4.2.5      | Stack overheads for ISR                | 25            |

|   |                 | 4.2.6      | ORTI/Lauterbach                        | 25            |

|   |                 | 4.2.7      | ORTI Stack Fill                        | 25            |

|   |                 | 4.2.8      | Enable stack repositioning             | 25            |

|   |                 | 4.2.9      | Enable untrusted stack check           | 26            |

|   |                 | 4.2.10     | CrossCore SGI0                         | 26            |

|   |                 | 4.2.11     | CrossCore SGI1                         | 26            |

|   |                 | 4.2.12     | CrossCore SGI2                         | 27            |

|   |                 | 4.2.13     | CrossCore SGI3                         | 27            |

|   |                 | 4.2.14     | Set floating-point mode                | 27            |

|   |                 | 4.2.15     | Block default interrupt                | 28            |

|   |                 | 4.2.16     | GetAbortStack always                   | 28            |

|   |                 | 4.2.17     | Set interrupt priority range           | 28            |

|   |                 | 4.2.18     | Read CoreID from GIC                   | 29            |

|   | 4.3             | Generate   | d Files                                | 29            |

| 5 | Port-Spo | ecific API |                                               | 31 |

|---|----------|------------|-----------------------------------------------|----|

|   | 5.1      | API Calls  |                                               | 31 |

|   |          | 5.1.1      | Os_InitializeGICGroup                         | 31 |

|   |          | 5.1.2      | Os InitializeVectorTable                      | 31 |

|   | 5.2      | Callbacks  |                                               | 32 |

|   |          | 5.2.1      | Os_Cbk_GetAbortStack                          | 32 |

|   |          | 5.2.2      | Os_Cbk_StartCore                              | 33 |

|   |          | 5.2.3      | Os_Cbk_StopCore                               | 35 |

|   | 5.3      | Macros .   |                                               | 36 |

|   |          | 5.3.1      | CAT1_ISR                                      | 36 |

|   |          | 5.3.2      | Os_Clear_x                                    | 37 |

|   |          | 5.3.3      | Os_DisableAllConfiguredInterrupts_CPUx        | 37 |

|   |          | 5.3.4      | Os_Disable_x                                  | 37 |

|   |          | 5.3.5      | Os_EnableAllConfiguredInterrupts_CPUx         | 38 |

|   |          | 5.3.6      | Os_Enable_x                                   | 38 |

|   |          | 5.3.7      | Os_IntChannel_x                               | 38 |

|   |          | 5.3.8      | Os_Set_Edge_Triggered_x                       | 39 |

|   |          | 5.3.9      | Os_Set_Level_Sensitive_x                      | 39 |

|   | 5.4      | Type Def   | initions                                      | 39 |

|   |          | 5.4.1      | Os_StackSizeType                              | 39 |

|   |          | 5.4.2      | Os_StackValueType                             | 40 |

| 6 | Toolchai | 'n         |                                               | 41 |

|   | 6.1      | Compiler   | Versions                                      | 41 |

|   |          | 6.1.1      | ARM DS-5 Ultimate Edition: ARM Compiler 6.6 . | 41 |

|   | 6.2      | Options ι  | used to generate this guide                   | 42 |

|   |          | 6.2.1      | Compiler                                      | 42 |

|   |          | 6.2.2      | Assembler                                     | 43 |

|   |          | 6.2.3      | Librarian                                     | 44 |

|   |          | 6.2.4      | Linker                                        | 44 |

|   |          | 6.2.5      | Debugger                                      | 45 |

| 7  | Hardwai      | re        |                                         | 47       |

|----|--------------|-----------|-----------------------------------------|----------|

|    | 7.1          | Supporte  | d Devices                               | 47       |

|    | 7.2          | Register  | Usage                                   | 47       |

|    |              | 7.2.1     | Initialization                          | 47       |

|    |              | 7.2.2     | Modification                            | 48       |

|    | 7.3          | Interrupt | S                                       | 49       |

|    |              | 7.3.1     | Interrupt Priority Levels               | 49       |

|    |              | 7.3.2     | Allocation of ISRs to Interrupt Vectors | 50       |

|    |              | 7.3.3     | Vector Table                            | 51       |

|    |              | 7.3.4     | Writing Category 1 Interrupt Handlers   | 52       |

|    |              | 7.3.5     | Writing Category 2 Interrupt Handlers   | 52       |

|    |              | 7.3.6     | Default Interrupt                       | 53       |

|    | 7.4          | Memory    | Model                                   | 53       |

|    | 7.5          | Processo  | r Modes                                 | 53       |

|    | 7.6          | Stack Ha  | ndling                                  | 54       |

|    | 7.7          | Processo  | r state when calling StartOS()          | 54       |

| 8  | Perform      | ance      |                                         | 55       |

|    | 8.1          | Measurer  | ment Environment                        | 55       |

|    | 8.2          | RAM and   | ROM Usage for OS Objects                | 55       |

|    |              | 8.2.1     | Single Core                             | 56       |

|    |              | 8.2.2     | Multi Core                              | 56       |

|    | 8.3          | Stack Usa | age                                     | 56       |

|    | 8.4          | Library M | Iodule Sizes                            | 57       |

|    |              | 8.4.1     | Single Core                             | 57       |

|    |              | 8.4.2     | Multi Core                              | 59       |

|    | 8.5          | Execution | n Time                                  | 62       |

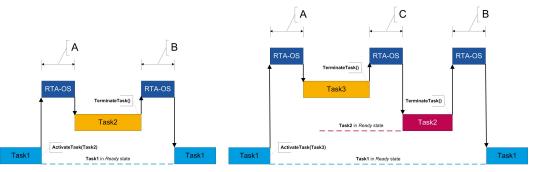

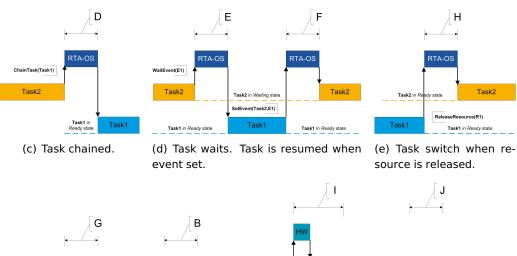

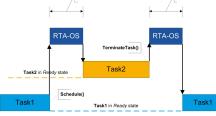

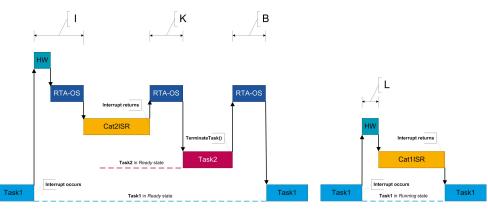

|    |              | 8.5.1     | Context Switching Time                  | 63       |

| 9  | Finding      | Out More  |                                         | 66       |

| 10 | Contacti     | ing ETAS  |                                         | 67       |

|    |              |           |                                         |          |

|    | 10.1         | Technical | Support                                 | 67       |

|    | 10.1<br>10.2 |           | l Support                               | 67<br>67 |

|    |              |           |                                         |          |

# 6 Contents

# 1 Introduction

RTA-OS is a small and fast real-time operating system that conforms to both the AUTOSAR OS (R3.0.1 -> R3.0.7, R3.1.1 -> R3.1.5, R3.2.1 -> R3.2.2, R4.0.1 -> R4.3.1) and OSEK/VDX 2.2.3 standards (OSEK is now standardized in ISO 17356). The operating system is configured and built on a PC, but runs on your target hardware.

This document describes the RTA-OS ZynqUSA53/ARM port plug-in that customizes the RTA-OS development tools for the Xilinx Zynq UltraScale+ Cortex-A53 with the ARM\_DS\_5\_V6 compiler. It supplements the more general information you can find in the *User Guide* and the *Reference Guide*.

The document has two parts. Chapters 2 to 3 help you understand the Zyn-qUSA53/ARM port and cover:

- how to install the ZynqUSA53/ARM port plug-in;

- how to configure ZynqUSA53/ARM-specific attributes;

- how to build an example application to check that the ZynqUSA53/ARM port plug-in works.

Chapters 4 to 8 provide reference information including:

- the number of OS objects supported;

- required and recommended toolchain parameters;

- how RTA-OS interacts with the Zynq UltraScale+ Cortex-A53, including required register settings, memory models and interrupt handling;

- memory consumption for each OS object;

- memory consumption of each API call;

- execution times for each API call.

For the best experience with RTA-OS it is essential that you read and understand this document.

#### 1.1About You

You are a trained embedded systems developer who wants to build real-time applications using a preemptive operating system. You should have knowledge of the C programming language, including the compilation, assembling and linking of C code for embedded applications with your chosen toolchain. Elementary knowledge about your target microcontroller, such as the start address, memory layout, location of peripherals and so on, is essential.

You should also be familiar with common use of the Microsoft Windows operating system, including installing software, selecting menu items, clicking buttons, navigating files and folders.

#### 1.2 **Document Conventions**

The following conventions are used in this guide:

| Choose File > Open.                   | Menu options appear in <b>bold, blue</b> characters.                                                                             |

|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| Click <b>OK</b> .                     | Button labels appear in <b>bold</b> characters                                                                                   |

| Press <enter>.</enter>                | Key commands are enclosed in angle brackets.                                                                                     |

| The "Open file" dialog<br>box appears | GUI element names, for example window titles, fields, etc. are enclosed in double quotes.                                        |

| Activate(Task1)                       | Program code, header file names, C type names,<br>C functions and API call names all appear in a<br>monospaced typeface.         |

| See Section 1.2.                      | Internal document hyperlinks are shown in blue letters.                                                                          |

| CS                                    | Functionality in RTA-OS that might not be portable<br>to other implementations of AUTOSAR OS is<br>marked with the RTA-OS icon.  |

| $\wedge$                              | Important instructions that you must follow care-<br>fully to ensure RTA-OS works as expected are<br>marked with a caution sign. |

#### Introduction 8

# 1.3 References

OSEK is a European automotive industry standards effort to produce open systems interfaces for vehicle electronics. OSEK is now standardized in ISO 17356. For details of the OSEK standards, please refer to:

#### http://www.osek-vdx.org

AUTOSAR (AUTomotive Open System ARchitecture) is an open and standardized automotive software architecture, jointly developed by automobile manufacturers, suppliers and tool developers. For details of the AUTOSAR standards, please refer to:

http://www.autosar.org

# 2 Installing the RTA-OS Port Plug-in

# 2.1 Preparing to Install

RTA-OS port plug-ins are supplied as a downloadable electronic installation image which you obtain from the ETAS Web Portal. You will have been provided with access to the download when you bought the port. You may optionally have requested an installation CD which will have been shipped to you. In either case, the electronic image and the installation CD contain identical content.

**Integration Guidance 2.1:** You must have installed the RTA-OS tools before installing the ZynqUSA53/ARM port plug-in. If you have not yet done this then please follow the instructions in the Getting Started Guide.

# 2.1.1 Hardware Requirements

You should make sure that you are using at least the following hardware before installing and using RTA-OS on a host PC:

- 1GHz Pentium Windows-capable PC.

- 2G RAM.

- 20G hard disk space.

- CD-ROM or DVD drive (Optional)

- Ethernet card.

# 2.1.2 Software Requirements

RTA-OS requires that your host PC has one of the following versions of Microsoft Windows installed:

- Windows 7

- Windows 8

- Windows 10

**Integration Guidance 2.2:** The tools provided with RTA-OS require Microsoft's .NET Framework v2.0 (included as part of .NET Framework v3.5) and v4.0 to be installed. You should ensure that these have been installed before installing RTA-OS. The .NET framework is not supplied with RTA-OS but is freely available from https: //www.microsoft.com/net/download. To install .NET 3.5 on Windows 10 see https://docs.microsoft.com/en-us/dotnet/framework/ install/dotnet-35-windows-10.

The migration of the code from v2.0 to v4.0 will occur over a period of time for performance and maintenance reasons.

# 10 Installing the RTA-OS Port Plug-in

# 2.2 Installation

Target port plug-ins are installed in the same way as the tools:

- 1. Either

- Double click the executable image; or

- Insert the RTA-OS ZynqUSA53/ARM CD into your CD-ROM or DVD drive.

If the installation program does not run automatically then you will need to start the installation manually. Navigate to the root directory of your CD/DVD drive and double click autostart.exe to start the setup.

2. Follow the on-screen instructions to install the ZynqUSA53/ARM port plug-in.

By default, ports are installed into C:\ETAS\RTA-OS\Targets. During the installation process, you will be given the option to change the folder to which RTA-OS ports are installed. You will normally want to ensure that you install the port plug-in in the same location that you have installed the RTA-OS tools. You can install different versions of the tools/targets into different directories and they will not interfere with each other.

**Integration Guidance 2.3:**Port plug-ins can be installed into any location, but using a non-default directory requires the use of the --target\_include argument to both **rtaosgen** and **rtaoscfg**. For example:

rtaosgen --target\_include:<target\_directory>

# 2.2.1 Installation Directory

The installation will create a sub-directory under Targets with the name ZynqUSA53ARM\_5.0.1. This contains everything to do with the port plug-in.

Each version of the port installs in its own directory - the trailing  $_5.0.1$  is the port's version identifier. You can have multiple different versions of the same port installed at the same time and select a specific version in a project's configuration.

The port directory contains:

ZynqUSA53ARM.dll - the port plug-in that is used by rtaosgen and rtaoscfg.

- **RTA-OS ZynqUSA53ARM Port Guide.pdf** the documentation for the port (the document you are reading now).

- **RTA-OS ZynqUSA53ARM Release Note.pdf** the release note for the port. This document provides information about the port plug-in release, including a list of changes from previous releases and a list of known limitations.

There may be other port-specific documentation supplied which you can also find in the root directory of the port installation. All user documentation is distributed in PDF format which can be read using Adobe Acrobat Reader. Adobe Acrobat Reader is not supplied with RTA-OS but is freely available from http://www.adobe.com.

# 2.3 Licensing

RTA-OS is protected by FLEXnet licensing technology. You will need a valid license key in order to use RTA-OS.

Licenses for the product are managed using the ETAS License Manager which keeps track of which licenses are installed and where to find them. The information about which features are required for RTA-OS and any port plug-ins is stored as license signature files that are stored in the folder <install\_folder>\bin\Licenses.

The ETAS License Manager can also tell you key information about your licenses including:

- Which ETAS products are installed

- Which license features are required to use each product

- Which licenses are installed

- When licenses expire

- Whether you are using a local or a server-based license

Figure 2.1 shows the ETAS License Manager in operation.

#### 2.3.1 Installing the ETAS License Manager

**Integration Guidance 2.4:**The ETAS License Manager must be installed for RTA-OS to work. It is highly recommended that you install the ETAS License Manager during your installation of RTA-OS.

The installer for the ETAS License Manager contains two components:

1. the ETAS License Manager itself;

# 12 Installing the RTA-OS Port Plug-in

| License                 | Product                 | Status        | Version | Source | Expiration Date |

|-------------------------|-------------------------|---------------|---------|--------|-----------------|

| ASCET-MD                | ASCET                   | INSTALLED     | 6.0     | SERVER | Permanent       |

| ASCET-RP                | ASCET                   | INSTALLED     | 6.0     | SERVER | Permanent       |

| ASCET-SE                | ASCET                   | INSTALLED     | 6.0     | SERVER | Permanent       |

| LD_RTA-OS3.0_PPCE200GHS | LD_RTA-OS3.0 PPCe200GHS | NOT AVAILABLE | 1.0     |        | No Information  |

| LD_RTA-OS3.0_SRC        | LD_RTA-OS3.0            | NOT AVAILABLE | 1.0     |        | No Information  |

| LD_RTA-OS3.0_VRTA       | LD_RTA-OS3.0 VRTA       | INSTALLED     | 1.0     | LOCAL  | 3-aug-2009      |

| LD_RTA-RTE2.1           | RTA-RTE2.1              | INSTALLED     | 1.0     | SERVER | Permanent       |

| •                       |                         |               |         |        | Þ               |

| ense Information        |                         |               |         |        | <u>×</u>        |

Figure 2.1: The ETAS License manager

a set of re-distributable FLEXnet utilities. The utilities include the software and instructions required to setup and run a FLEXnet license server manager if concurrent licenses are required (see Sections 2.3.2 and 2.3.3 for further details)

During the installation of RTA-OS you will be asked if you want to install the ETAS License Manager. If not, running install it manually at a later time you can by <install\_folder>\LicenseManager\LicensingStandaloneInstallation.exe.

Once the installation is complete, the ETAS License Manager can be found in C:\Program Files\Common Files\ETAS\Licensing.

After it is installed, a link to the ETAS License Manager can be found in the Windows Start menu under **Programs**  $\rightarrow$  **ETAS**  $\rightarrow$  **License Management**  $\rightarrow$  **ETAS License Manager**.

#### 2.3.2 Licenses

When you install RTA-OS for the first time the ETAS License Manager will allow the software to be used in *grace mode* for 14 days. Once the grace mode period has expired, a license key must be installed. If a license key is not available, please contact your local ETAS sales representative. Contact details can be found in Chapter 10.

You should identify which type of license you need and then provide ETAS with the appropriate information as follows:

**Machine-named licenses** allows RTA-OS to be used by any user logged onto the PC on which RTA-OS and the machine-named license is installed.

A machine-named license can be issued by ETAS when you provide the host ID (Ethernet MAC address) of the host PC

**User-named licenses** allow the named user (or users) to use RTA-OS on any PC in the network domain.

A user-named license can be issued by ETAS when you provide the Windows user-name for your network domain.

**Concurrent licenses** allow any user on any PC up to a specified number of users to use RTA-OS. Concurrent licenses are sometimes called *floating* licenses because the license can *float* between users.

A concurrent license can be issued by ETAS when you provide the following information:

- 1. The name of the server

- 2. The Host ID (MAC address) of the server.

- 3. The TCP/IP port over which your FLEXnet license server will serve licenses. A default installation of the FLEXnet license server uses port 27000.

You can use the ETAS License Manager to get the details that you must provide to ETAS when requesting a machine-named or user-named license and (optionally) store this information in a text file.

Open the ETAS License Manager and choose **Tools**  $\rightarrow$  **Obtain License Info** from the menu. For machine-named licenses you can then select the network adaptor which provides the Host ID (MAC address) that you want to use as shown in Figure 2.2. For a user-based license, the ETAS License Manager automatically identifies the Windows username for the current user.

Selecting "Get License Info" tells you the Host ID and User information and lets you save this as a text file to a location of your choice.

#### 2.3.3 Installing a Concurrent License Server

Concurrent licenses are allocated to client PCs by a FLEXnet license server manager working together with a vendor daemon. The vendor daemon for ETAS is called ETAS.exe. A copy of the vendor daemon is placed on disk when you install the ETAS License Manager and can be found in:

C:\Program Files\Common Files\ETAS\Licensing\Utility

#### 14 Installing the RTA-OS Port Plug-in

| Name                                                                     | MAC Address | IP Address             |

|--------------------------------------------------------------------------|-------------|------------------------|

| Intel(R) PRO/Wireless 3945ABG Netw<br>Broadcom NetXtreme Gigabit Etherne |             | 0.0.0.0<br>10.103.6.34 |

Figure 2.2: Obtaining License Information

To work with an ETAS concurrent license, a license server must be configured which is accessible from the PCs wishing to use a license. The server must be configured with the following software:

- FLEXnet license server manager;

- ETAS vendor daemon (ETAS.exe);

It is also necessary to install your concurrent license on the license server.

In most organizations there will be a single FLEXnet license server manager that is administered by your IT department. You will need to ask your IT department to install the ETAS vendor daemon and the associated concurrent license.

If you do not already have a FLEXnet license server then you will need to arrange for one to be installed. A copy of the FLEXnet license server, the ETAS vendor daemon and the instructions for installing and using the server (LicensingEndUserGuide.pdf) are placed on disk when you install the ETAS License manager and can be found in:

C:\Program Files\Common Files\ETAS\Licensing\Utility

# 2.3.4 Using the ETAS License Manager

If you try to run the RTA-OS GUI **rtaoscfg** without a valid license, you will be given the opportunity to start the ETAS License Manager and select a license. (The command-line tool **rtaosgen** will just report the license is not valid.)

| License           | Product      | Status        | Version | Source | Expiration Date | Borrow Expiration Date |

|-------------------|--------------|---------------|---------|--------|-----------------|------------------------|

| LD_RTA-OS3.0_SRC  | LD_RTA-OS3.0 | NOT AVAILABLE | 1.0     |        | No Information  |                        |

| LD_RTA-OS3.0_VRTA | LD_RTA-053.0 | NOT AVAILABLE | 1.0     |        | No Information  |                        |

|                   |              |               |         |        |                 |                        |

|                   |              |               |         |        |                 |                        |

|                   |              |               |         |        |                 |                        |

|                   |              |               |         |        |                 |                        |

| se Information    |              |               |         |        |                 |                        |

| se Information    |              |               |         |        |                 |                        |

| e Information     |              |               |         |        |                 | ]                      |

Figure 2.3: Unlicensed RTA-OS Installation

When the ETAS License Manager is launched, it will display the RTA-OS license state as NOT AVAILABLE. This is shown in Figure 2.3.

Note that if the ETAS License Manager window is slow to start, **rtaoscfg** may ask a second time whether you want to launch it. You should ignore the request until the ETAS License Manager has opened and you have completed the configuration of the licenses. You should then say yes again, but you can then close the ETAS License Manager and continue working.

#### License Key Installation

License keys are supplied in an ASCII text file, which will be sent to you on completion of a valid license agreement.

If you have a machine-based or user-based license key then you can simply install the license by opening the ETAS License Manager and selecting File  $\rightarrow$  Add License File menu.

If you have a concurrent license key then you will need to create a license stub file that tells the client PC to look for a license on the FLEXnet server as follows:

- 1. create a copy of the concurrent license file

- 2. open the copy of the concurrent license file and delete every line *except* the one starting with SERVER

- 3. add a new line containing USE\_SERVER

- 4. add a blank line

# 16 Installing the RTA-OS Port Plug-in

| License          | Product         | Status    | Version | Source | Expiration Date | Borrow Expiration Date |

|------------------|-----------------|-----------|---------|--------|-----------------|------------------------|

| LD_RTA-OS3.0_SR  | C LD_RTA-OS3.0  | INSTALLED | 1.0     | LOCAL  | 24-dec-2008     |                        |

| LD_RTA-OS3.0_VR  | TA LD_RTA-OS3.0 | INSTALLED | 1.0     | LOCAL  | 24-dec-2008     |                        |

| 1                |                 |           |         |        |                 |                        |

| 11/2             |                 |           |         |        |                 |                        |

| ense Information |                 |           |         |        |                 | 2                      |

Figure 2.4: Licensed features for RTA-OS

5. save the file

The file you create should look something like this:

```

SERVER <server name> <MAC address> <TCP/IP Port>¶

USE_SERVER¶

¶

```

Once you have create the license stub file you can install the license by opening the ETAS License Manager and selecting **File**  $\rightarrow$  **Add License File** menu and choosing the license stub file.

```

License Key Status

```

When a valid license has been installed, the ETAS License Manager will display the license version, status, expiration date and source as shown in Figure 2.4.

Borrowing a concurrent license

If you use a concurrent license and need to use RTA-OS on a PC that will be disconnected from the network (for example, you take a demonstration to a customer site), then the concurrent license will not be valid once you are disconnected.

To address this problem, the ETAS License Manager allows you to temporarily borrow a license from the license server.

To borrow a license:

- 1. Right click on the license feature you need to borrow.

- 2. Select "Borrow License"

- 3. From the calendar, choose the date that the borrowed license should expire.

- 4. Click "OK"

The license will automatically expire when the borrow date elapses. A borrowed license can also be returned before this date. To return a license:

- 1. Reconnect to the network;

- 2. Right-click on the license feature you have borrowed;

- 3. Select "Return License".

#### 2.3.5 Troubleshooting Licenses

RTA-OS tools will report an error if you try to use a feature for which a correct license key cannot be found. If you think that you should have a license for a feature but the RTA-OS tools appear not to work, then the following troubleshooting steps should be followed before contacting ETAS:

#### Can the ETAS License Manager see the license?

The ETAS License Manager must be able to see a valid license key for each product or product feature you are trying to use.

You can check what the ETAS License Manager can see by starting it from the **Help**  $\rightarrow$  **License Manager...** menu option in **rtaoscfg** or directly from the Windows Start Menu - **Start**  $\rightarrow$  **ETAS**  $\rightarrow$  **License Management**  $\rightarrow$  **ETAS License Manager**.

The ETAS License Manager lists all license features and their status. Valid licenses have status INSTALLED. Invalid licenses have status NOT AVAILABLE.

#### Is the license valid?

You may have been provided with a time-limited license (for example, for evaluation purposes) and the license may have expired. You can check that the Expiration Date for your licensed features to check that it has not elapsed using the ETAS License Manager.

If a license is due to expire within the next 30 days, the ETAS License Manager will use a warning triangle to indicate that you need to get a new license. Figure 2.5 shows that the license features LD\_RTA-0S3.0\_VRTA and LD\_RTA-0S3.0\_SRC are due to expire.

If your license has elapsed then please contact your local ETAS sales representative to discuss your options.

#### 18 Installing the RTA-OS Port Plug-in

|      | icense                 | Product                 | Status        | Version      | Source | Expiration Date |

|------|------------------------|-------------------------|---------------|--------------|--------|-----------------|

| 🕗 A  | ASCET-SE               | ASCET                   | INSTALLED     | 6.0          | SERVER | Permanent       |

| ۵ 🗘  | D_RTA-OS3.0_PPCE200GHS | LD_RTA-OS3.0 PPCe200GH5 | NOT AVAILABLE | 1.0          |        | No Information  |

| ۱ L  | D_RTA-OS3.0_SRC        | LD_RTA-OS3.0            | INSTALLED     | 1.0          | LOCAL  | 24-dec-2008     |

| 1 L  | D_RTA-OS3.0_VRTA       | LD_RTA-OS3.0 VRTA       | INSTALLED     | 1.0          | LOCAL  | 24-dec-2008     |

| 🕗 L  | D_RTA-RTE2.1           | RTA-RTE2.1              | INSTALLED     | 1.0          | SERVER | Permanent       |

|      | Information            |                         |               | - Alexandria |        |                 |

| ense | Information            |                         |               |              |        | *               |

|      |                        |                         |               |              |        |                 |

|      |                        |                         |               |              |        |                 |

Figure 2.5: Licensed features that are due to expire

#### Does the Ethernet MAC address match the one specified?

If you have a machine based license then it is locked to a specific MAC address. You can find out the MAC address of your PC by using the ETAS License Manager (**Tools**  $\rightarrow$  **Obtain License Info**) or using the Microsoft program **ipconfig /all** at a Windows Command Prompt.

You can check that the MAC address in your license file by opening your license file in a text editor and checking that the HOSTID matches the MAC address identified by the ETAS License Manager or the *Physical Address* reported by **ipconfig /all**.

If the HOSTID in the license file (or files) does not match your MAC address then you do not have a valid license for your PC. You should contact your local ETAS sales representative to discuss your options.

#### Is your Ethernet Controller enabled?

If you use a laptop and RTA-OS stops working when you disconnect from the network then you should check your hardware settings to ensure that your Ethernet controller is not turned off to save power when a network connection is not present. You can do this using Windows Control Panel. Select **System**  $\rightarrow$  **Hardware**  $\rightarrow$  **Device Manager** then select your Network Adapter. Right click to open **Properties** and check that the Ethernet controller is not configured for power saving in **Advanced** and/or **Power Management** settings.

#### Is the FlexNet License Server visible?

If your license is served by a FlexNet license server, then the ETAS License Manager will report the license as NOT AVAILABLE if the license server cannot be accessed.

You should contact your IT department to check that the server is working correctly.

#### Still not fixed?

If you have not resolved your issues, after confirming these points above, please contact ETAS technical support. The contact address is provided in Section 10.1. You must provide the contents and location of your license file and your Ethernet MAC address.

# 3 Verifying your Installation

Now that you have installed both the RTA-OS tools and a port plug-in and have obtained and installed a valid license key you can check that things are working.

# 3.1 Checking the Port

The first thing to check is that the RTA-OS tools can see the new port. You can do this in two ways:

# 1. use the **rtaosgen** tool

You can run the command **rtaosgen** --**target**: to get a list of available targets, the versions of each target and the variants supported, for example:

RTA-OS Code Generator Version p.q.r.s, Copyright © ETAS nnnn Available targets: TriCoreHighTec\_n.n.n [TC1797...] VRTA\_n.n.n [MinGW,VS2005,VS2008,VS2010]

2. use the **rtaoscfg** tool

The second way to check that the port plug-in can be seen is by starting **rtaoscfg** and selecting **Help**  $\rightarrow$  **Information...** drop down menu. This will show information about your complete RTA-OS installation and license checks that have been performed.

**Integration Guidance 3.1:** If the target port plug-ins have been installed to a non-default location, then the --target\_include argument must be used to specify the target location.

If the tools can see the port then you can move on to the next stage – checking that you can build an RTA-OS library and use this in a real program that will run on your target hardware.

# 3.2 Running the Sample Applications

Each RTA-OS port is supplied with a set of sample applications that allow you to check that things are running correctly. To generate the sample applications:

- 1. Create a new *working* directory in which to build the sample applications.

- 2. Open a Windows command prompt in the new directory.

3. Execute the command:

```

rtaosgen --target:<your target> --samples:[Applications]

e.g.

rtaosgen --target:[MPC5777Mv2]PPCe200HighTec_5.0.8

--samples:[Applications]

```

You can then use the build.bat and run.bat files that get created for each sample application to build and run the sample. For example:

```

cd Samples\Applications\HelloWorld

build.bat

run.bat

```

Remember that your target toolchain must be accessible on the Windows PATH for the build to be able to run successfully.

**Integration Guidance 3.2:** It is strongly recommended that you build and run at least the Hello World example in order to verify that RTA-OS can use your compiler toolchain to generate an OS kernel and that a simple application can run with that kernel.

For further advice on building and running the sample applications, please consult your *Getting Started Guide*.

# 4 **Port Characteristics**

This chapter tells you about the characteristics of RTA-OS for the Zyn-qUSA53/ARM port.

# 4.1 Parameters of Implementation

To be a valid OSEK (ISO 17356) or AUTOSAR OS, an implementation must support a minimum number of OS objects. The following table specifies the *minimum* numbers of each object required by the standards and the *maximum* number of each object supported by RTA-OS for the ZynqUSA53/ARM port.

| Parameter                        | Required | RTA-OS     |

|----------------------------------|----------|------------|

| Tasks                            | 16       | 1024       |

| Tasks not in SUSPENDED state     | 16       | 1024       |

| Priorities                       | 16       | 1024       |

| Tasks per priority               | -        | 1024       |

| Queued activations per priority  | -        | 4294967296 |

| Events per task                  | 8        | 32         |

| Software Counters                | 8        | 4294967296 |

| Hardware Counters                | -        | 4294967296 |

| Alarms                           | 1        | 4294967296 |

| Standard Resources               | 8        | 4294967296 |

| Linked Resources                 | -        | 4294967296 |

| Nested calls to GetResource()    | -        | 4294967296 |

| Internal Resources               | 2        | no limit   |

| Application Modes                | 1        | 4294967296 |

| Schedule Tables                  | 2        | 4294967296 |

| Expiry Points per Schedule Table | -        | 4294967296 |

| OS Applications                  | -        | 4294967295 |

| Trusted functions                | -        | 4294967295 |

| Spinlocks (multicore)            | -        | 4294967295 |

| Register sets                    | -        | 4294967296 |

# 4.2 Configuration Parameters

Port-specific parameters are configured in the **General**  $\rightarrow$  **Target** workspace of **rtaoscfg**, under the "Target-Specific" tab.

The following sections describe the port-specific configuration parameters for the ZynqUSA53/ARM port, the name of the parameter as it will appear in the XML configuration and the range of permitted values (where appropriate).

#### 4.2.1 Stack used for C-startup

XML name SpPreStartOS

The amount of stack already in use at the point that StartOS() is called. This value is simply added to the total stack size that the OS needs to support all tasks and interrupts at run-time. Typically you use this to obtain the amount of stack that the linker must allocate. The value does not normally change if the OS configuration changes.

4.2.2 Stack used when idle

#### XML name SpStartOS

# Description

The amount of stack used when the OS is in the idle state (typically inside Os\_Cbk\_Idle()). This is just the difference between the stack used at the point that Os\_StartOS() is called and the stack used when no task or interrupt is running. This can be zero if Os\_Cbk\_Idle() is not used. It must include the stack used by any function called while in the idle state. The value does not normally change if the OS configuration changes.

4.2.3 Stack overheads for ISR activation

XML name SplDisp

#### Description

The extra amount of stack needed to activate a task from within an ISR. If a task is activated within a Category 2 ISR, and that task has a higher priority than any currently running task, then for some targets the OS may need to use marginally more stack than if it activates a task that is of lower priority. This value accounts for that. On most targets this value is zero. This value is used in worst-case stack size calculations. The value may change if significant changes are made to the OS configuration. e.g. STANDARD/EXTENDED, SC1/2/3/4.

4.2.4 Stack overheads for ECC tasks

XML name SpECC

# Description

The extra amount of stack needed to start an ECC task. ECC tasks need to save slightly more state on the stack when they are started than BCC tasks. This value contains the difference. The value may change if significant changes are made to the OS configuration. e.g. STANDARD/EXTENDED, SC1/2/3/4.

#### 4.2.5 Stack overheads for ISR

#### XML name SpPreemption

#### Description

The amount of stack used to service a Category 2 ISR. When a Category 2 ISR interrupts a task, it usually places some data on the stack. If the ISR measures the stack to determine if the preempted task has exceeded its stack budget, then it will overestimate the stack usage unless this value is subtracted from the measured size. The value is also used when calculating the worst-case stack usage of the system. Be careful to set this value accurately. If its value is too high then when the subtraction occurs, 32-bit underflow can occur and cause the OS to think that a budget overrun has been detected. The value may change if significant changes are made to the OS configuration. e.g. STANDARD/EXTENDED, SC1/2/3/4.

#### 4.2.6 ORTI/Lauterbach

#### XML name Orti22Lauterbach

#### Description

Select ORTI generation for the Lauterbach debugger.

#### Settings

| Value | Description       |

|-------|-------------------|

| true  | Generate ORTI     |

| false | No ORTI (default) |

#### 4.2.7 ORTI Stack Fill

XML name OrtiStackFill

#### Description

Expands ORTI information to cover stack address, size and fill pattern details to support debugger stack usage monitoring.

#### Settings

| Value | Description                               |

|-------|-------------------------------------------|

| true  | Support ORTI stack tracking               |

| false | ORTI stack tracking unsupported (default) |

# 4.2.8 Enable stack repositioning

**XML name** AlignUntrustedStacks

Use to support realignment of the stack for untrusted code when there are MPU protection region granularity issues. Refer to the documentation for Os\_Cbk\_SetMemoryAccess.

#### Settings

| Value | Description               |

|-------|---------------------------|

| true  | Support repositioning     |

| false | Normal behavior (default) |

#### 4.2.9 Enable untrusted stack check

XML name DistrustStacks

#### Description

Extra code can be placed in interrupt handlers to detect when untrusted code has an illegal stack pointer value. Also exception handlers run on a private stack (Refer to the documentation for Os\_Cbk\_GetAbortStack). This has a small performance overhead, so is made optional. When enabled 32 bytes of EL1 stack are required for each core.

#### Settings

| Value | Description            |

|-------|------------------------|

| true  | Perform the checks     |

| false | Do not check (default) |

#### 4.2.10 CrossCore SGI0

XML name CrossCoreSGI0

# Description

Optionally specify the SGI used for cross-core interrupts for core 0. A free SGI will be selected automatically if one is not specified. Used in multicore applications only.

#### Settings

| Value      | Description                                         |

|------------|-----------------------------------------------------|

| CPU0 GIC0  | Lowest SGI for CPU0                                 |

| CPU0 GIC15 | Highest SGI for CPU0 (all values between are valid) |

#### 4.2.11 CrossCore SGI1

XML name CrossCoreSGI1

#### 26 Port Characteristics

Optionally specify the SGI used for cross-core interrupts for core 1. A free SGI will be selected automatically if one is not specified. Used in multicore applications only.

#### Settings

| Value      | Description                                         |

|------------|-----------------------------------------------------|

| CPU1 GIC0  | Lowest SGI for CPU1                                 |

| CPU1 GIC15 | Highest SGI for CPU1 (all values between are valid) |

#### 4.2.12 CrossCore SGI2

XML name CrossCoreSGI2

#### Description

Optionally specify the SGI used for cross-core interrupts for core 2. A free SGI will be selected automatically if one is not specified. Used in multicore applications only.

#### Settings

| Value      | Description                                         |

|------------|-----------------------------------------------------|

| CPU2 GIC0  | Lowest SGI for CPU2                                 |

| CPU2 GIC15 | Highest SGI for CPU2 (all values between are valid) |

# 4.2.13 CrossCore SGI3

| XML | name | CrossCoreSGI3 |

|-----|------|---------------|

|     |      |               |

# Description

Optionally specify the SGI used for cross-core interrupts for core 3. A free SGI will be selected automatically if one is not specified. Used in multicore applications only.

#### Settings

| Value      | Description                                         |

|------------|-----------------------------------------------------|

| CPU3 GIC0  | Lowest SGI for CPU3                                 |

| CPU3 GIC15 | Highest SGI for CPU3 (all values between are valid) |

#### 4.2.14 Set floating-point mode

XML name FloatingPointMode

Enable or disable hardware floating-point instructions. Used in the compiler command line option -mcpu to select the optional architectural feature for floating-point mode extensions to the instruction set.

# Settings

| Value | Description                                |

|-------|--------------------------------------------|

| nofp  | Code does not use floating-point (default) |

| fp    | Floating-point instructions generated      |

# 4.2.15 Block default interrupt

**XML name** block\_default\_interrupt

# Description

Where a default interrupt is specified, it will normally execute if an unexpected (i.e. unused) interrupt triggers. This option changes this behavior by lowering the priority assigned to unused interrupt sources. When selected the default interrupt handler will be blocked by higher priority code.

#### Settings

| Value | Description                                                        |

|-------|--------------------------------------------------------------------|

| true  | Block the default interrupt                                        |

| false | Allow the default interrupt handler to run if an unexpected inter- |

|       | rupt fires (default)                                               |

# 4.2.16 GetAbortStack always

XML name always\_call\_GetAbortStack

# Description

When an unexpected interrupt/exception or memory protection violation occurs always use the Os\_Cbk\_GetAbortStack() callback to set up a safe area of memory to use as a stack executing the ProtectionHook (please refer to the documentation for Os\_Cbk\_GetAbortStack).

# Settings

| Value | Description                                                 |

|-------|-------------------------------------------------------------|

| true  | Always call Os_Cbk_GetAbortStack()                          |

| false | Only call Os_Cbk_GetAbortStack() when the 'Enable untrusted |

|       | stack check' target option is selected (default)            |

# 4.2.17 Set interrupt priority range

**XML name** InterruptPriorityRange

#### 28 Port Characteristics

Select the range of priorities used by the Generic Interrupt Controller (GIC) for Software Generated Interrupts (SGIs), Private Peripheral Interrupts (PPIs), or Shared Peripheral Interrupts (SPIs). If applications are run in the non-secure state then the GIC only supports 16 priority levels and this option should be set accordingly.

# Settings

| Value | Description                                   |

|-------|-----------------------------------------------|

| 16    | 4 bit GIC interrupt priority values           |

| 32    | 5 bit GIC interrupt priority values (default) |

# 4.2.18 Read CoreID from GIC

XML name read\_CoreID\_from\_GIC

#### Description

In untrusted code the RTA-OS by default uses an SVC call to identify the current CPU core from the MPIDR\_EL1 register. Selecting this option causes RTA-OS to to identify the CPU core from the memory mapped register GICD\_ITARGETSR0 instead. This improves the performance of untrusted code by removing the need for an expensive synchronous exception. Since this isn't necessary for trusted code the option is ignored if no untrusted code is present. If selected the MMU must allow untrusted code read access for the GIC registers.

# Settings

| Value | Description                   |

|-------|-------------------------------|

| true  | Read from GIC                 |

| false | Read from MPIDR_EL1 (default) |

# 4.3 Generated Files

The following table lists the files that are generated by **rtaosgen** for all ports:

| Filename                        | Contents                                                   |

|---------------------------------|------------------------------------------------------------|

| Os.h                            | The main include file for the OS.                          |

| Os_Cfg.h                        | Declarations of the objects you have configured.           |

|                                 | This is included by 0s.h.                                  |

| Os_MemMap.h                     | AUTOSAR memory mapping configuration used by               |

|                                 | RTA-OS to merge with the system-wide MemMap.h              |

|                                 | file in AUTOSAR versions 4.0 and earlier. From AU-         |

|                                 | TOSAR version 4.1, $0s_MemMap.h$ is used by the OS         |

|                                 | instead of MemMap.h.                                       |

| RTAOS. <lib></lib>              | The RTA-OS library for your application. The exten-        |

|                                 | sion <lib> depends on your target.</lib>                   |

| RTAOS. <lib>.sig</lib>          | A signature file for the library for your application.     |

|                                 | This is used by <b>rtaosgen</b> to work out which parts of |

|                                 | the kernel library need to be rebuilt if the configu-      |

|                                 | ration has changed. The extension <lib> depends</lib>      |

|                                 | on your target.                                            |

| <projectname>.log</projectname> | A log file that contains a copy of the text that the       |

|                                 | tool and compiler sent to the screen during the            |

|                                 | build process.                                             |

# 5 Port-Specific API

The following sections list the port-specific aspects of the RTA-OS programmers reference for the ZynqUSA53/ARM port that are provided either as:

- additions to the material that is documented in the Reference Guide; or

- overrides for the material that is documented in the *Reference Guide*. When a definition is provided by both the *Reference Guide* and this document, the definition provided in this document takes precedence.

# 5.1 API Calls

# 5.1.1 Os\_InitializeGICGroup

Initialize the GIC GICD\_IGROUPRx registers.

#### Syntax

void Os\_InitializeGICGroup(void)

# Description

Os\_InitializeGICGroup() is available when the GIC will be used in the non-secure state. All GIC interrupts are configured as Group 1 (non-secure) interrupts

Os\_InitializeGICGroup() should be called when the CPU is in the secure state before StartOS(). If the application is to be run in the secure state then Os\_InitializeGICGroup() need not be called. In multi-core applications it should be called by all cores. It should be called even if 'Suppress Vector Table Generation' is set to TRUE. Os\_InitializeVectorTable() should also be called to configure the other GIC registers.

# Example

Os\_InitializeGICGroup();

# See Also

Os\_InitializeVectorTable StartOS

# 5.1.2 Os\_InitializeVectorTable

Initialize the GIC GICD\_IPRIORITYRx, GICD\_ISENABLERx/GICD\_ICENABLERx, OS\_GICD\_ITARGETSRx, and VBAR\_EL1 registers.

#### Syntax

void Os\_InitializeVectorTable(void)

#### Description

Os\_InitializeVectorTable() initializes the GIC GICD\_IPRIORITYRx, GICD\_ISENABLERx/GICD\_ICENABLERx, and OS\_GICD\_ITARGETSRx according to the requirements of the project configuration. The GIC priority is set to block Category 2 interrupts and allow Category 1 interrupts. FIQ and IRQ interrupts are also enabled

When the CPU is run in the secure state the GICD\_IGROUPx registers are also initialized.

Os\_InitializeVectorTable() should be called before StartOS(). In multi-core applications it should be called by all cores. It should be called even if 'Suppress Vector Table Generation' is set to TRUE.

#### Example

Os\_InitializeVectorTable();

#### See Also

Os\_InitializeGICGroup StartOS

- 5.2 Callbacks

- 5.2.1 Os\_Cbk\_GetAbortStack

Callback routine to provide the start address of the stack to use to handle exceptions.

#### Syntax

FUNC(void \*,OS\_APPL\_CODE) Os\_Cbk\_GetAbortStack(void)

#### **Return Values**

The call returns values of type **void** \*.

Untrusted code can misbehave and cause a protection exception. When this happens, AUTOSAR requires that ProtectionHook is called and the task, ISR or OS Application must be terminated.

It is possible that at the time of the fault the stack pointer is invalid. For this reason, if 'Enable untrusted stack check' is configured, RTA-OS will call Os\_Cbk\_GetAbortStack to get the address of a safe area of memory that it should use for the stack while it performs this processing.

Maskable interrupts will be disabled during this process so the stack only needs to be large enough to perform the ProtectionHook.

A default implementation of Os\_Cbk\_GetAbortStack is supplied in the RTA-OS library that will place the abort stack at the starting stack location of the untrusted code.

In systems that use the Os\_Cbk\_SetMemoryAccess callback, the return value is the last stack location returned in ApplicationContext from Os\_Cbk\_SetMemoryAccess. This is to avoid having to reserve memory. Note that this relies on Os\_Cbk\_SetMemoryAccess having been called at least once on that core otherwise zero will be returned. (The stack will not get adjusted if zero is returned.) Otherwise the default implementation returns the address of an area of static memory that is reserved for sole use by the abort stack.

# Example

```

FUNC(void *,0S_APPL_CODE) 0s_Cbk_GetAbortStack(void) {

/* 64-bit alignment is needed for EABI. */

static long long abortstack[40U] __attribute__((aligned (16)));

return &abortstack[40U];

}

```

#### **Required when**

The callback must be present if 'Enable untrusted stack check' is configured and there are untrusted OS Applications. The callback is also present if the 'GetAbortStack always' target option is enabled.

#### 5.2.2 Os\_Cbk\_StartCore

Callback routine used to start a non-master core on a multi-core variant.

#### Syntax

```

FUNC(StatusType, {memclass})Os_Cbk_StartCore(

uint16 CoreID

)

```

# **Return Values**

The call returns values of type StatusType.

| Value   | Build | Description                                    |

|---------|-------|------------------------------------------------|

| E_0K    | all   | No error.                                      |

| E_OS_ID | all   | The core does not exist or can not be started. |

#### Description

In a multi-core application, the StartCore or StartNonAutosarCore OS APIs have to be called prior to StartOS for each core that is to run. For this target port, these APIs make a call to Os\_Cbk\_StartCore() which is responsible for starting the specified core.

RTA-OS provides a default implementation of Os\_Cbk\_StartCore() that will be appropriate for most normal situations. To support multi-core applications the caches and SCU must be enabled in all cores otherwise data coherency cannot be maintained between cores. Os\_Cbk\_StartCore() does not get called for core 0,

Note: memclass is OS\_APPL\_CODE for AUTOSAR 3.x, OS\_CALLOUT\_CODE for AUTOSAR 4.0, OS\_OS\_CBK\_STARTCORE\_CODE for AUTOSAR 4.1.

#### Example

```

FUNC(StatusType, {memclass}) Os_Cbk_StartCore(uint16 CoreID)

{

StatusType ret = E_OS_ID;

volatile uint32 *0s_CoreStartPtr = (volatile uint32

*)&Os_StartCoreFlags;

/* If not the primary core. */

if (CoreID != 0U) {

/* Issue a SEV instruction to signal an event to all PEs to

wake-up a

* secondary core. Events can be triggered by the debugger

and semi-hosting

* so additionally use a variable to signal that RTA-OS is

waking-up a

* specific core. This is reset once the core is awake. */

*(Os_CoreStartPtr + CoreID) = 0xA0U;

__asm volatile("dsb SY" : : : "memory", "cc");

__asm volatile("sev" : : : "memory", "cc");

/* Wait for the core to wake up by monitoring the variable

value */

while (*(0s_CoreStartPtr + CoreID) == 0xA0U) {

__asm volatile("dsb SY" : : : "memory", "cc");

__asm volatile("nop" : : : "memory", "cc");

```

```

__asm volatile("nop" : : : "memory", "cc");

__asm volatile("nop" : : : "memory", "cc");

}

ret = E_OK;

}

return ret;

```

# **Required when**

Required for non-master cores that will be started.

#### See Also

}

StartCore StartNonAutosarCore StartOS

# 5.2.3 Os\_Cbk\_StopCore

Callback routine used to stop a non-master core on a multi-core variant.

#### Syntax

```

FUNC(StatusType, {memclass})Os_Cbk_StopCore(

uint16 CoreID

)

```

# **Return Values**

The call returns values of type StatusType.

| Value   | Build | Description                                    |

|---------|-------|------------------------------------------------|

| E_0K    | all   | No error.                                      |

| E_OS_ID | all   | The core does not exist or can not be started. |

# Description

Each non-master (secondary) core should call Os\_Cbk\_StopCore() before entering OS\_MAIN(). This will cause the core to pause. When the primary master core calls Os\_Cbk\_StartCore() the stopped core will be released and will continue execution. Os\_Cbk\_StopCore() should be used before the primary master core uses the StartCore() or StartOS() API calls.

RTA-OS provides a default implementation of Os\_Cbk\_StopCore() that will be appropriate for most normal situations. To support multi-core applications

the caches and SCU must be enabled in all cores otherwise data coherency is not maintained between cores. Os\_Cbk\_StopCore() should not get called for core 0 as this is the primary master core.

Note: memclass is OS\_APPL\_CODE for AUTOSAR 3.x, OS\_CALLOUT\_CODE for AUTOSAR 4.0, OS\_OS\_CBK\_STOPCORE\_CODE for AUTOSAR 4.1.

#### Example

```

FUNC(StatusType, {memclass}) Os_Cbk_StopCore(uint16 CoreID)

{

volatile uint32 *0s_CoreStartPtr = (volatile uint32

*)&Os_StartCoreFlags;

/* If an expected core, shutdown until the value in

0s_StartCoreFlags[] holds

* a value set by Os_Cbk_StartCore() for this core */

while (*(Os_CoreStartPtr + CoreID) != 0xA0U) {

/* Issue a WFE instruction to put the secondary core into a

low power state.

* Note starting other cores, debug and semihosting events

can cause a SEV

* to wake-up the core. Check if it is valid to wake-up this

core. */

__asm volatile("wfe" : : : "memory", "cc")

}

/* Reset the variable to let core 0 know that the core has

started. */

*(Os_CoreStartPtr + CoreID) = 0x0U;

__asm volatile("dsb SY" : : : "memory", "cc");

return E_OK;

}

```

#### **Required when**

Required for non-master cores that will be started.

#### See Also

StartCore StartNonAutosarCore StartOS

# 5.3 Macros

# 5.3.1 CAT1\_ISR

Macro that should be used to create a Category 1 ISR entry function. This should only be used on Category 1 ISRs that are attached to the Generic

#### 36 Port-Specific API

Interrupt Controller (GIC) not the Cortex CPU exceptions (See the later section on "Writing Category 1 Interrupt Handlers" for more information). This macro exists to help make your code portable between targets.

#### Example

CAT1\_ISR(MyISR) {...}

#### 5.3.2 Os\_Clear\_x

Use of the Os\_Clear\_x macro will clear the interrupt request bit of the GICD\_ICPEND register for the named interrupt channel. The macro can be called using either the GIC channel number or the RTA-OS configured vector name. In the example, this is Os\_Clear\_GIC48() and Os\_Clear\_Millisecond() respectively. To use the Os\_Clear\_x macro the file Os\_ConfigInterrupts.h must be included through the use of #include. The macro is provided so the interrupt channel can be cleared without corrupting the interrupt priority value configured by calling Os\_InitializeVectorTable(). It may not be used by untrusted code.

#### Example

Os\_Clear\_GIC48()

Os\_Clear\_Millisecond()

5.3.3 Os\_DisableAllConfiguredInterrupts\_CPUx

The Os\_DisableAllConfiguredInterrupts\_CPUx macro will disable all configured GIC interrupt channels on CPUx (where x = 0 to 3). In the example, this is CPU0. To use the Os\_DisableAllConfiguredInterrupts\_CPUx macro the file Os\_ConfigInterrupts.h must be included through the use of #include. The macro is provided so the interrupt channels can be disabled without corrupting the interrupt priority values configured by calling Os\_InitializeVectorTable(). It may not be used by untrusted code.

#### Example

Os\_DisableAllConfiguredInterrupts\_CPU0()

...

Os\_EnableAllConfiguredInterrupts\_CPU0()

### 5.3.4 Os\_Disable\_x

Use of the Os\_Disable\_x macro will disable the named interrupt channel. The macro can be called using either the GIC channel number or the RTA-OS configured vector name. In the example, this is Os\_Disable\_GIC48() and Os\_Disable\_Millisecond() respectively. To use the Os\_Disable\_x macro the file Os\_ConfigInterrupts.h must be included through the use of #include. The macro is provided so the interrupt channel can be masked without corrupting the interrupt priority value configured by calling Os\_InitializeVectorTable(). It may not be used by untrusted code.

#### Example

Os\_Disable\_GIC48()

Os\_Disable\_Millisecond()

#### 5.3.5 Os\_EnableAllConfiguredInterrupts\_CPUx

The Os\_EnableAllConfiguredInterrupts\_CPUx macro will enable all configured EI interrupt channels on CPUx (where x = 0 to 3). In the example, this is CPU0. To use the Os\_EnableAllConfiguredInterrupts\_CPUx macro the file Os\_ConfigInterrupts.h must be included through the use of #include. The macro is provided so the interrupt channels can be enabled without corrupting the interrupt priority values configured by calling Os\_InitializeVectorTable(). It may not be used by untrusted code.

#### Example

. . .

Os\_DisableAllConfiguredInterrupts\_CPU0()

Os\_EnableAllConfiguredInterrupts\_CPU0()

### 5.3.6 Os\_Enable\_x

Use of the Os\_Enable\_x macro will enable the named interrupt channel. The macro can be called using either the GIC channel number or the RTA-OS configured vector name. In the example, this is Os\_Enable\_GIC48() and Os\_Enable\_Millisecond() respectively. To use the Os\_Enable\_x macro the file Os\_ConfigInterrupts.h must be included through the use of #include. The macro is provided so the interrupt channel can be enabled without corrupting the interrupt priority value configured by calling Os\_InitializeVectorTable(). It may not be used by untrusted code.

#### Example

Os\_Enable\_GIC48()

Os\_Enable\_Millisecond()

## 5.3.7 Os\_IntChannel\_x

The Os\_IntChannel\_x macro can be used to get the vector number associated with the named GIC interrupt (0, 1, 2...). The macro can be called using either the GIC vector name or the RTA-OS configured vector name. In the example, this is Os\_IntChannel\_Parity\_Core\_0 and Os\_IntChannel\_Millisecond respectively. To use the Os\_IntChannel\_x macro the file Os\_ConfigInterrupts.h must be included through the use of #include. On a multi-core CPU GIC interrupts on different cores may have the same vector number. This is because the

#### 38 Port-Specific API

GIC maintains a copy of interrupts 0 to 31 for each CPU core. Those outside this range share a single copy between all CPU cores.

#### Example

trigger\_interrupt(Os\_IntChannel\_TPU); trigger\_interrupt(Os\_IntChannel\_Millisecond);

#### 5.3.8 Os\_Set\_Edge\_Triggered\_x

Use of the Os\_Set\_Edge\_Triggered\_x macro will configure the named GIC interrupt channel as Edge-triggered. The macro can be called using either the channel name or the RTA-OS configured vector name. In the example, this is Os\_Set\_Edge\_Triggered\_GIC32() and Os\_Set\_Edge\_Triggered\_Millisecond() respectively. Only GIC channels 32 and above can be modified; the other channels have fixed settings. To use the Os\_Set\_Edge\_Triggered\_x macro the file Os\_ConfigInterrupts.h must be included through the use of #include. It may not be used by untrusted code.

#### Example

Os\_Set\_Edge\_Triggered\_GIC32()

Os\_Set\_Edge\_Triggered\_Millisecond()

#### 5.3.9 Os\_Set\_Level\_Sensitive\_x

Use of the Os\_Set\_Level\_Sensitive\_x macro will configure the named GIC interrupt channel as Level-sensitive. The macro can be called using either the channel name or the RTA-OS configured vector name. In the example, this is Os\_Set\_Level\_Sensitive\_GIC32() and Os\_Set\_Level\_Sensitive\_Millisecond() respectively. Only GIC channels 32 and above can be modified; the other channels have fixed settings. To use the Os\_Set\_Level\_Sensitive\_x macro the file Os\_ConfigInterrupts.h must be included through the use of #include. It may not be used by untrusted code.

#### Example

Os\_Set\_Level\_Sensitive\_GIC32()

Os\_Set\_Level\_Sensitive\_Millisecond()

### 5.4 Type Definitions

#### 5.4.1 Os\_StackSizeType

An unsigned value representing an amount of stack in bytes.

#### Example

```

Os_StackSizeType stack_size;

stack_size = Os_GetStackSize(start_position, end_position);

```

5.4.2 Os\_StackValueType

An unsigned value representing the position of the stack pointer (USR/SYS mode).

#### Example

```

Os_StackValueType start_position;

start_position = Os_GetStackValue();

```

# 6 Toolchain

This chapter contains important details about RTA-OS and the ARM\_DS\_5\_V6 toolchain. A port of RTA-OS is specific to both the target hardware and a specific version of the compiler toolchain. You must make sure that you build your application with the supported toolchain.

In addition to the version of the toolchain, RTA-OS may use specific tool options (switches). The options are divided into three classes:

kernel options are those used by rtaosgen to build the RTA-OS kernel.

**mandatory** options must be used to build application code so that it will work with the RTA-OS kernel.

forbidden options must not be used to build application code.

Any options that are not explicitly forbidden can be used by application code providing that they do not conflict with the kernel and mandatory options for RTA-OS.

**Integration Guidance 6.1:**ETAS has developed and tested RTA-OS using the tool versions and options indicated in the following sections. Correct operation of RTA-OS is only covered by the warranty in the terms and conditions of your deployment license agreement when using identical versions and options. If you choose to use a different version of the toolchain or an alternative set of options then it is your responsibility to check that the system works correctly. If you require a statement that RTA-OS works correctly with your chosen tool version and options then please contact ETAS to discuss validation possibilities.

### 6.1 Compiler Versions

This port of RTA-OS has been developed to work with the following compiler(s):

### 6.1.1 ARM DS-5 Ultimate Edition: ARM Compiler 6.6

Ensure that armclang.exe is on the path and that the appropriate environment variables have been set.

### Tested on ARM Compiler 6.6

If you require support for a compiler version not listed above, please contact ETAS.

#### 6.2 Options used to generate this guide

#### 6.2.1 Compiler

Namearmclang.exeVersionComponent: ARM Compiler 6.6

#### Options

#### **Kernel Options**

The following options were used to build the RTA-OS kernel for the configuration that was used to generate the performance figures in this document. If you select different target options, then the values used to build the kernel might change. You can run a Configuration Summary report to check the values used for your configuration.

- --target=aarch64-arm-none-eabi Generates A64 instructions for AArch64 state

- -fno-vectorize Disables generation of Advanced SIMD vector instructions

- -mcpu=cortex-a53+nocrc+nocrypto+nofp+nosimd Target the Cortex-A53

architecture and additional features including the floating-point mode

(value set by target option)

- -mno-unaligned-access Disable unaligned access to data

- -Ofast Set fast optimization level

- -std=gnull 2011 C standard code with GNU extensions

- -fms-extensions Enable the compiler extensions for section use pragmas

#### **Mandatory Options for Application Code**

The following options were mandatory for application code used with the configuration that was used to generate the performance figures in this document. If you select different target options, then the values required by application code might change. You can run a Configuration Summary report to check the values used for your configuration.

- The same options as for compilation

#### 42 Toolchain

### Forbidden Options for Application Code

The following options were forbidden for application code used with the configuration that was used to generate the performance figures in this document. If you select different target options, then the forbidden values might change. You can run a Configuration Summary report to check the values used for your configuration.

- -fshort-enums Set the size of an enumeration type to the smallest data type

- -fvectorize Generate Advanced SIMD vector instructions

- -mbig-endian Generate big-endian code

- -munaligned-access Enable unaligned access to data

- -std=x Other C standard code apart from gnull

- --target=arm-arm-none-eab Generates A32/T32 instructions for AArch32 state

- Any other options that conflict with kernel options

#### 6.2.2 Assembler

Namearmclang.exeVersionComponent: ARM Compiler 6.6

Options

### **Kernel Options**

The following options were used to build the RTA-OS kernel for the configuration that was used to generate the performance figures in this document. If you select different target options, then the values used to build the kernel might change. You can run a Configuration Summary report to check the values used for your configuration.

- The same options as for compilation

### **Mandatory Options for Application Code**

The following options were mandatory for application code used with the configuration that was used to generate the performance figures in this document. If you select different target options, then the values required by application code might change. You can run a Configuration Summary report to check the values used for your configuration.

- The same options as for compilation

#### **Forbidden Options for Application Code**

The following options were forbidden for application code used with the configuration that was used to generate the performance figures in this document. If you select different target options, then the forbidden values might change. You can run a Configuration Summary report to check the values used for your configuration.

- Any options that conflict with kernel options

#### 6.2.3 Librarian

Namearmar.exeVersionComponent: ARM Compiler 6.6

#### 6.2.4 Linker

Namearmlink.exeVersionComponent: ARM Compiler 6.6

#### Options

#### **Kernel Options**

The following options were used to build the RTA-OS kernel for the configuration that was used to generate the performance figures in this document. If you select different target options, then the values used to build the kernel might change. You can run a Configuration Summary report to check the values used for your configuration.

- --info=totals, sizes, unused Specify map file contents

- --datacompressor=off Disable RW data compression

- --noremove Do not remove unused input sections

- --xref Output cross reference information to the map file

- --map Output memory map to the map file

- --symbols Output symbol table to the map file

- --verbose Output detailed information to the map file

- --entry=reset\_handler Specify the application entry point

### **Mandatory Options for Application Code**